Chip-Scale-Packages (CSPs) sind für die Applikation speziell in mobilen Geräten sehrattraktiv, weil sie nur etwa ein Fünftel größer sind als der nackte Die. Seit längerer Zeit verarbeitet Flextronics, einer der führenden Fertigungsdienstleister, diese Bausteine und hat zu deren Evaluierung in der Baugruppenfertigung sogenannte Test-Vehikel oder Test-Schaltungen entwickelt. Auf der Basis dieser Evaluie-rungsschaltung werden Probleme und Herausforderungen in der CSP-Applikation untersucht, einschließlich der Entwicklung und Optimierung von Produktionsprozessen sowie deren Schlüsselvariablen.

Kazu Nakajima, Alington Lewis, Ravi Bhat und Sammy YiFlextronics International Ltd., San Jose,Kalifornien

Elektronik wird laufend kompakter. Insbesondere durch die tragbaren, äußerst kleinen Geräte in der Telekommunikation, Computertechnik usw. ist ein großer Bedarf an stetig kleinere Bauelemente entstanden. Chip-Scale-Packages bieten sich als optimale Lösung an, denn sie ermöglichen sehr hohe Packungsdichte bei sehr geringen Bauelementegrößen. Als einer der führenden globalen Dienstleister in der Elektronikfertigung, der natürlich auch über hohe Kompetenz in Entwicklung und Engineering verfügt, untersucht Flextronics den Einsatz von CSPs schon seit einigen Jahren intensiv. Denn damit konnte man wirtschaftliche und zuverlässige Produktionsprozesse entwickeln und optimieren. Außerdem ist es wichtig, den Auftraggebern nachzuweisen, wie man auch in diesen Techniken zuverlässige Lötstellen/Interconnections bereitstellt. Wichtig ist auch noch, praxisnahe Regeln für das Boarddesign und den Engineeringaufgaben im Prozeß bzw. seiner Kontrollezu erarbeiten – bis hin zur Gestaltungder Pastendruckschablonen. Und letztlich muß die CSP-Baugruppenmontage auch noch in die SMT-Fertigung implementiert werden.

Das erste Test-Vehikel für den CSP-Einsatz, eingesetzt vor einigen Jahren, hatte das Format einer PCMCIA-Karte und enthielt sieben CSPs von vier Herstellern, beidseitig bestückt mit SMDs und COB-Komponenten, aber keinen CSPs. Die zweite, jetzt entwickelte Testschaltung für die nächste Bausteingeneration baut auf den Erfahrungen auf und hat ebenfalls PCMCIA-Format (Bild 1). Sie enthält jedoch 18 unterschiedliche CSPs von 12 Lieferanten. Hinzu kommen SMDs sowie kleine diskrete Bauelemente wie 0201 bzw. 0402, die wie die CSPs auf beiden Baugruppenseiten bestückt sind.

Finepitch-Trends

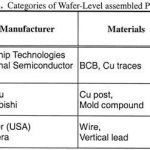

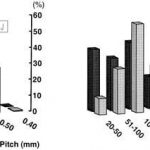

JEDEC und EIJA haben vor kurzem unter ihren Mitgliedern eine Befragung über die laufenden Aktivitäten bei der Anwendung von Finepitch-Komponenten durchgeführt, bezogen auf die Strukturen der Ball-Grid-Arrays. Die zusammengefaßten Daten der Erhebung (Bild 2) zeigen wie sich der Trend in der Industrie verhält, wobei hier der Pincount sowie die Rastermaße der Grid-Array-Bauteile im Vordergrund stehen. Deutlich wird, das Rastermaß von 0,6 mm dominiert sowohl in der JEDEC- als auch EIJA-Untersuchung, dabei ist insgesamt der Bereich zwischen 0,5 bis 0,8 mm am wichtigsten.

Die JEDEC-Mitglieder haben ihren Schwerpunkt beim 0,75-mm-Raster und einem relativ geringen Pincount. Weniger als 50 Anschlüsse und ein Pitch von 0,75 mm sind typisch für Flashspeicher. DieEIJA-Mitglieder hingegen verwenden CSPs mit Pitchmaßen von 0,5 und 0,8 mm und relativ hohem Pincount, sogar mehr als 300 Anschlüsse. Solch ein Baustein mit hoher Pinzahl kann ein Rambus-Speicher sein, gestapelte ICs (Stacking), DSPs, ASICs usw. Die Ergebnisse der Studien zeigen, daß der 0,5-mm-Pitch und höhere Anschlußzahlen in Grid-Array-Packages am häufigsten eingesetzt werden.

Wafer-Level-Packages

Packages auf Wafer-Level (WLP) waren vor einigen Jahren noch, als die erste Testschaltung implementiert wurde, eine absolute Rarität. Zu dieser Zeit (1997) war nur eine Ausführung verfügbar, die dann später auch rasch obsolet wurde. Inzwischen wurden weitere WLPs entwickelt und ih-re baldige Verfügbarkeit angekündigt.Einige WLP-Ausführungen, einschließlich UltraCSP, Super CSP, MAG und SICSPsind mit Daisy-Chain-Strukturen für Testzwecke ausgestattet.

Komponentenauswahl

Auf Basis der Erfahrungen mit dem ersten Test-Vehikel wurden zur Qualifikation mehrere Arten von CSPs im Pitch-Bereich von 05 bis 0,8 mm ausgewählt. Deren Padgrößen liegen zwischen 0,15 bis 0,8 mm und die Anschlußzahlen zwischen 4 bis 308. Bauteile wurden auch danach ausgewählt, ob Muster mit Daisy-Chain-Strukturen für Testzwecke verfügbar sind.

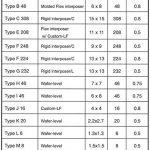

Die neue Testschaltung weist 18 CSPs in 14 unterschiedlichen Strukturen von 12 Herstellern auf. Die CSP-Typen A bis C haben die gleiche Ausführung wie auf demersten Test-Vehikel. Zwei Flex-Interposer weisen 46 bzw. 188 I/Os auf (Typ A), ein vergossener Flex-Interposer (Typ B) hat48 Anschlüsse. Ein starrer CSP-Interposer aus Keramik (Typ C) ist ein Land-Grid-Array (LGA) mit ursprünglich 324 Anschlüssen, sein Pad-Array wurde für 308 Pins modifiziert. Ein Wafer-Level-Package (Typ D), verwendet beim ersten Mal, ist veraltet. Typ E ist kategorisiert als Flex-Interposer, doch besteht der Supportrahmen aus LF-Material (Keramik). Der CSP-Typ F weist 248 bzw. 224 Anschlüsse auf und ist auf einem starren Keramik-Interposer aufgebracht und enthält Solderballs. Diese Keramik-Interposer (Type C und F) bestehen aus LTCC-Material (Low Temperature Co-fired Ceramic).

Typ G ist ein typischer Fineline-PBGA mit niedrigem Profil. Die Ausführungen H und I mit 46 Anschlüssen und ebenso Typ A 46 sind für die gleiche Art von Produkt konzipiert, beispielsweise Flashspeicher. Dennoch haben diese drei CSPs unterschiedliche Strukturen: es handelt sich um einen Flex-Interposer und zwei Wafer-Level-Bausteine. Andere Wafer-Level-Packages auf dieser Testschaltung haben relativ niedrigen Pincount (4 bis 20), so wie die Ausführungen K, L und M. Die Ausführungen J mit 16 und O mit 24 Anschlüssen in kundenspezifischem LF-Material und Typ N mit 24 und 28 I/Os auf starrem Laminat weisen ebenfalls einen niedrigen Pincount auf. Sie werden kommerziell als Peripherie-ICs (kleine Gehäuse mit niedrigem Profil) eingesetzt. Die Lötstellen/Interconnects aller CSPs sind per Daisy-Chain-Strukturen elektrisch kontaktierbar. Außerdem konnte jeder Lötanschluß anhand der um jeden IC oder auf der Rückseite des Boards gruppierten Testpads einzeln geprüft werden.

Design desTest-Vehikels

Das Test-Board war im Format der PC Card Typ II entwickelt worden. Damit es in dieses Format paßt, hat der Print eine Breite von 72 mm und eine Länge von 48 mm (Dicke 0,5 mm). Hier waren auch die nötigen Flächen für die Steckverbindungen an beiden schma-len Enden sowieeinige Bohrungen und Platinenausbrüche für das Karten-Assembly berücksichtig worden. Der Hauptsteckverbinder der PC Card ist eine Version mit 68 Pin, daneben wurde noch ein 25-Pin-Steckverbinder untergebracht. Weil sehr viele Arten von Bauelementen eingesetzt wurden, hat man sie in zwei unterschiedliche PC Cards (Ausführungen A und B) aufgeteilt.

Für die erste Testschaltung wurden Standard-Designrules der Industrie angewendet, beispielsweise 4mil (100 Mikron) Leiterbahnen und Abstände sowie 8/15 mil (200/375 Mikron) für die Bohrungen und Pads der minimalen Durchkontaktierungen auf doppelseitigen FR4-Leiterplatten. Die zweite Testschaltung war unter relativ anspruchsvollen Designrules realisiert worden, beispielsweise 3/3 mil (75 Mikron) Leiterbahnen und Abstände sowie 8/12 mil (200/300 Mikron) für die kleinsten Bohrungen und Pads auf einem vierlagigen FR4-Board. Diese Designrules stellen für herkömmliche SMT-Fertigungslinien erhebliche Herausforderungen dar. In Übereinstimmung mit früheren Unter-suchungen wurden NSDM-Paddesigns (Non Solder Mask Defined) angewendet. Die Padgröße hatte die gleichen Abmessungen wie das dazu korrespondierende Pad auf dem CSP (1:1 Paddesign), davon gab es nur einige Ausnahmen. Die Oberfläche des Test-Vehikels erhielt eine Hauchvergoldung über Nickel.

Die zweite Testschaltung wurde mit Hilfe mehrerer experimenteller Evaluierungen entwickelt. Zum einen tragen die Boards A und B auf beiden SeitenCSPs (die erste Schaltung nur auf einer Seite). Zum anderen sind einige CSP-Montageplätze auf beiden Seiten gespiegelt. Einer dieser Montageplätze ist um eine halbe Packageabmessung verschoben, während der Rest sich auf dem gleichen Platz befindet, allerdings auf der gegenüberliegende Seite. Zudem wurden einige kleine Komponenten anders untergebracht. Ein Bestückbereich wurdeoffen angelegt, während ein anderer nahe an großen Bauelementen plaziert wurde. Denn damit läßt sich herausfinden, ob die große thermische Masse großer Bauteile während des Reflowprozeß die kleinen Komponenten wesentlich beeinflußt.

Schablonendesign

Schwierig war die Optimierung des Lot-pastendrucks. Geringere Pitchabstände und Padabmessungen der CSPs führen im Pastendruck zu einem höheren Grad von Komplexität. Zum Absichern einer zuverlässigen CSP-Montage müssen Höhe und Volumen der Lotpaste exakt kontrolliert werden. Jedoch reagieren CSPs mit Solderballs, die nicht umgedreht werden dürfen sowie solche mit LGA-Struktur empfindlicher auf aufgedruckte Pastenvolumen. Hier werden die Lötstellen ausschließlich von der aufgedruckten Paste gebildet. Die angewendeten Designregeln für Schablonen basieren auf den Empfehlungen eines Flextronics-Projekts für die Optimierung von CSP-Printing. Ein wichtiges Tool in dieser Studie über den Lotpastendruck war eine 125 Mikron dicke Schablone, lasergeschnitten und elektrisch poliert. In der ersten Studie über die CSP-Implementation war die gleiche Schablonenart verwendet worden. Ein Hauptgrund für den Einsatz einer lasergeschnittenen Schablone war der Bedarf für konische und trape-zoide Formen mit großen Öffnungen auf der Schablonenunterseite. Diese Öffnungen mit Abschrägungen von ungefähr 5° sorgen für ausgezeichneten Pastentransfer auf die Leiterplatte, insbesondere bei Druck von Finepitch- sowie kleinen Bauteilstrukturen.

Zudem werden mit dem Elektropolieren kleine Rauhigkeiten auf den Innenseiten der Schablonenöffnungen beseitigt. Dies führt zu einer glatten Oberfläche und einem gleichmäßigen Pastendruck ohne Schmiereffekte. Ein wichtiger Parameter für die Schablone ist die Area-Ratio, definiert als der Bereich (Area) der Öffnung dividiert durch die Summe der Innenseiten. Eine Area-Ratio über 0,5 wurde in dieser Studie angewendet, denn damit wurde ein konstanter Pastendruck für Finepitch-Strukturen mit kleinen Öffnungen erreicht. Außerdem wurde eine rechteckige Apertur für Bereiche mit kleinem Area-Ratio eingesetzt. Diese rechteckige Öffnung verbessert die Konstanz des Pastenvolumens, insbesondere bei sehr feinen Öffnungen.

Prozess-entwicklung

Unser Team für die Prozeßimplementierung setzt sich aus Mitarbeitern aus Prozeßentwicklung, Fertigungsengineering sowie Design- und Prototypen-Engineering zusammen. Die Prozeßimplementierung, auch die Entwicklung von Montageprozessen für CSPs auf Baugruppen, besteht grundsätzlich aus folgenden fünfAbschnitten:

• Prozeßcharakterisierung

• Vorläufige Evaluierung

• Prozeßtest

• Prozeßbestätigung

• Qualifikation

Die Prozeßcharakterisierung umfaßt zwei Schritte: die erste Evaluierung sowie die eigentliche Prozeßcharakterisierung. Die erste Evaluierung dient der Untersuchung jedes einzelnen Prozeßschritts und der Definition, welche Parameter die Schlüsselvariablen sind. In der Prozeßcharakterisierung werden die grundlegenden Abläufe Pastendruck, Bestückung (Pick&Place) undReflowlöten untersucht und definiert. Die vorläufige Evaluierung dient zur Spezifizierung des Basisprozeß in der Fertigung. Die Parameter des Produktionsprozeß’ wurden anhand der Ergebnisse aus der Prozeßevaluierung optimiert. Optische Inspektion, elektrische Prüfungen und Studien über die Prozeßfähigkeit wurden vorgenommen, um die Prozeßparameter für die nächste Phase vorzubereiten.

Mit diesen optimierten Prozeßparametern konnte der Prozeßtest durchgeführt werden, der einer Prozeßbestätigung voraus- geht. Ziel des Prozeßtests ist, den Prozeß auf der Fertigungslinie zu verifizieren, die dann in der Lage ist, Testschaltungenfür die Qualifikation zu fertigen. An-schließend kann die Prozeßbestätigung erfolgen, dieser Durchgang erfolgt mit den optimierten und vorgeprüften Parametern. In dieser Phase prüft man, ob die Prozeß-Performance gleichmäßig ist und in der evaluierten Fertigung zuverlässig Testschaltungen hergestellt werden. Während der Prozeßbestätigung sendet man unter anderem solche Baugruppen an unabhängige Prüflabors für Zuverlässigkeitstests zur Qualifikation. In dieser Studie konnte die Prozeßcharakterisierung übersprungen werden, denn die erste Implementierung der CSP-Montage auf Boards hatte bereits stattgefunden. Bild 3 zeigt den Ablauf der Prozeßentwicklung für die CSP-Montage.

Lotpastendruck

Für den Lotpastendruck verwendeten wir die verbesserte Formulierung einer eutektischen No-Clean-Paste (Pb63/Sn37) mit der Pulverfraktion Nummer 4 (Lotpulvergröße 25 bis 38 Mikron, Meshgröße-400/+500). In dieser Lotpaste wird als Flußmittel ein modifiziertes Kolophonium mit höherer Aktivierung für bessere Benetzung verwendet. Diese Lotpaste hat ausgezeichnete Fineline-Druckeigenschaften mit sauber definierten Lotdepots, hohe Druckgeschwindigkeit und beste Benetzungseigenschaften. Die No-Clean-Paste wurde ausgewählt, um halogenhaltige Rückstände sowie zusätzliche Reinigungsprozeduren zu vermeiden, die im Falle von wasserlöslichen Pasten nötig sind. Zum Druck wurde ein typischer Pastendrucker mit Metallrakel verwendet.

Pick&Place-Bestückung

Die Pick&Place-Bestückung wurde mit einem Highspeed-Chipshooter und einem Fine-pitch-Placer durchgeführt. Der Chipshooter wurde für die relativkleinen Komponenten einschließlich Diskrete (0201) sowie kleine CSPs mit geringem Pincount eingesetzt, die auf Tape&Reel zur Verfügung gestellt werden. DieFinepitch-Maschine enthält ein hochauf-lösendes Visionsystem, womit exakte Pick&Place-Vorgänge sowohl aus Stangen als auch Reels durchgeführt werden können. Die meisten CSPs stehen in kundenspezifischen JEDEC-Trays zur Verfügung oder Tape& Reels, das sind adäquate Verpackungsformen für Pick& Place. Einige CSPs wurden in fehlerhaft konzipierten Trays ausgeliefert, die zu unzuverlässigen Bestückvorgängen führten.

Reflowlöten

Der hier benutzte Vollkonvektions-Reflowofen ist ähnlich zu jenen in typischen SMT-Fertigungen. Aufgrund der Erfahrung mit CSP-Baugruppen haben wir auf einem Profiling-Board nahe den Lötstellen an jeder Bauteilseite Thermopaare plaziert. Damit konnten wir Daten für ein adäquates Lötprofil mit präziser Temperaturführung gewinnen. Diese Temperaturmessungen sowie ihre Aufzeichnung sind wichtig, denn die Reflowprofile in einem Ofen bestimmen die Qualität der Lötstellen. Doch entziehen sich die zwischen dem Bauteil und der Leiterplatte liegenden Lötstellen dervisuellen Beurteilung.

Der primäre Fehlereffekt einer CSP-Lötstelle zum Board ist die Materialermüdung. Die Hauptfaktoren, die die Zuverlässigkeit der CSP-Lötstellen beeinflussen, sind Temperaturen und die Differenzen in den thermischen Ausdehnungskoeffizienten zwischen dem CSP-Substrat (Silizium, Keramik usw.) und dem Board (Epoxy- oder Glasfasermaterial). Zum Evaluieren der Zuverlässigkeit unseres CSP-Montage wurde das Testboard einer Reihe von beschleunigten Streß- bzw. Alterungsprüfungen ausgesetzt.

Ergebnisse

Der Lotpastendruck wurde für die Prozeßbestätigung evaluiert und gezielt auf den Prozeß abgestimmt, Basis waren die Empfehlungen aus dem Projekt für die Optimierung des CSP-Printingprozeß. Die optimierten Druckparameter und die ordentlich gestaltete Schablone erbrachten gute Resultate und somit erreichten wir durch die Evaluierung und Prozeßbestätigung einen Cpk von 1,6 und besser. Anhand der typischen Lotdepotformen konnten wir einen konsistenten und gut kontrollierten Pastendruck bei unterschiedlichen CSP-Ausführungen nachweisen. Bild 4 zeigt solche Lotdepots wie Wafer-Level-Package (Typ M, 4 Pads, Pitch 0,5 mm); Finepitch-Area-Array (Type F, 248 Pads, Pitch 0,5 mm), Large-Area-Array (Type C), 308 Pads, Pitch 0,8 mm) sowie periphere Pad-Konfiguration (Type N, 24 Pads, Pitch0,5 mm).

Mit dem Pick&Place-Prozeß gab es keine gravierenden Probleme, ausgenommen davon waren einige Bausteinstangen, die nicht das passende Format aufwiesen. Dies war schon ein Problem bei der Bestückung unseres ersten Testboards.Tape&Reel-Zuführung ist zu empfehlen, denn damit lassen sich exakte Pick&Place-Vorgänge durchführen. Für relativ große Komponenten sind kundenspezifische JEDEC-Trays vorteilhaft. Der ideale Tray soll konstantes und genaues Positionieren der CSP unterstützen, damit die Lotkugeln unter dem CSP nicht beschädigt werden. Der Chipshooter konnte kleinere Bauteile sauber plazieren, einschließlich CSPs und kleine Diskrete. Für eine CSP-Ausführung jedoch, Wafer-Level-Package Typ M mit geringen Abmessungen, ist die Finepitch-Maschine mit Visionsystem nötig. Dieses Bauteil mit glänzender Unterseite weisteinen geringen Kontrast zwischen dieser reflektierenden Oberfläche und den Lotkugeln auf. Deshalb ist das hochauflösende Visionsystem hilfreich bei der Erkennung der Balls. Auf dem Chipshooter führte dieser reduzierte Kontrast zu Fehlerausrichtungen (Bild 5).

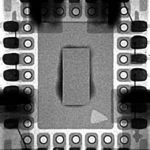

Nach dem Reflowlöten wurde die Rönt-geninspektion vorgenommen und Kreuzschliffe angefertigt (Bild 6). Deutlich wird, daß die Komponenten korrekt ausgerichtet und die Lötstellen gut ausgebildet sind. Das Reflowprofil für die No-Clean-Paste wurde mit dem bereits beschriebenen Profilingboard ermittelt. Dieses Profil ist weist typische Temperaturgradienten von 1,0 bis 1, 2 K/s während des Aufheizens auf, eine Zeitspannen zwischen 46 bis 52 s überLiquidus und eine Peaktemperatur zwischen 201 bis 212°C.

Neben den erwähnten 18 CSPs war die zweite Testschaltung auch mit SMDs wie QFP, TSOP und 0201 beidseitig bestückt. Die Komponenten wurden anhand deraktuellen Bauelemente/Packaging-Tends ausgewählt, wie Wafer-Level-Versionen, weiter reduzierte Bauformen sowie geringerer Pincount. Ähnliches gilt auch für das Leiterplattendesign mit seinen reduzierten Strukturen. Zudem implementierten wir mehrere experimentelle Evaluierungen in das Test-Vehikel, dazu gehören doppelseitige CSPs, gespiegelte CSPs mit akuraten Pad-zu-Pad-Ausrichtung sowie mit Split-Pad-Alignment usw. Weitere wichtigeFeature sind ein Area-Ratio mit 0,5 sowie der Prozeßindex Cpk 1,6. Auch die ge-laserte und elektropolierte Schabloneverhilft zu hoher Prozeßsicherheit. Nicht übersehen werden darf zudem der Ein-fluß des Bestückers und der Bauteilzuführung.

Mit diesem Projekt zur Prozeßentwicklung für den Einsatz von CSPs auf Baugruppen werden wir auch die Haupteinflüsse auf die Bauteilmontage verifizieren. Wir nehmen dazu eine Schlußqualifikation derBoards in Zusammenarbeit mit unserer Projektgruppe für den Finepitch-Lot-pastendruck vor. Die Zuverlässigkeitsprüfungen finden anschließend statt, Ziel ist hier, Daten über die Zuverlässigkeit der Schaltungen und über Fehlermecha-nismen über längere Zeitabschnitte zu gewinnen.

EPP 218

Unsere Webinar-Empfehlung

Auch dieses Jahr präsentiert Koh Young wieder aktuelle Trends und „State of the Art“ Technologie aus der optischen Inspektion und 3D-Messung auf der Productronica in München. Aber wir alle kennen das Problem voller Terminkalender, Reisebeschränkungen oder fehlender Zeit, um in…

Teilen:

.png)