Die Chipmontage wird oft als wichtiger Faktor für die Ausbeute an Gehäuse-Bauelementen und deren Zuverlässigkeit angesehen. Der Trend zu immer kleineren und komplexeren Gehäusen setzt jedoch die Einhaltung immer engerer Toleranzen für die Montage des Chips auf dem Gehäusesubstrat voraus. Gefragt sind daher besonders leistungsfähige Chipmontagesysteme. Das Bonden mit sehr geringen Kräften stellt eine Lösung zur Einhaltung der engen Toleranzen dar, mit denen neue Maßstäbe bezüglich Klebeschichttoleranzen in der Bonding-Industrie möglich werden.

Harald Körber, Datacon GmbH, Radfeld

Ein auffallender Trend in der Elektronikindustrie ist der stets zunehmende Bedarf an noch leichteren und kleineren kabellosen Kommunikationsgeräten, die noch mehr Funktionen zu immer niedrigeren Kosten bieten sollen. Die IC-Hersteller allein können mit diesem Tempo nicht mehr Schritt halten, indem sie Technologien zur Integration mehrerer Millionen Transistoren auf einem einzigen Chip entwickeln, der mit Frequenzen im Gigahertz-Bereich arbeitet und nur noch geringste Leistungen aufnimmt. Auch die Gehäusetechnologie ist inzwischen zur unverzichtbaren Komponente für die Produktion dieser modernen Consumer-Elektronik geworden.

Angesichts der Tatsache, dass diese kleinen, mit sehr komplexen Funktionen ausgestatteten Systeme die Integration kompletter Single-Chip-Systeme oder Systeme in einem einzigen Gehäuse (System in Package – SiP) erfordern, sind an die Gehäuse entsprechend strengere Anforderungen zu stellen. Die Fähigkeit, Chips präzise aufeinander (stack die applications) oder eng nebeneinander platzieren zu können, wird mit zunehmender Miniaturisierung immer wichtiger. Ebenso die Verarbeitung zu Gehäusegrößen, die maximal 20% größer, als die Chipgröße sein dürfen (Chip-Scale-Packages, CSPs) erweist sich als wichtige Forderung des Marktes, um dem unaufhaltsamen Bestreben nach Miniaturisierung nachkommen zu können.

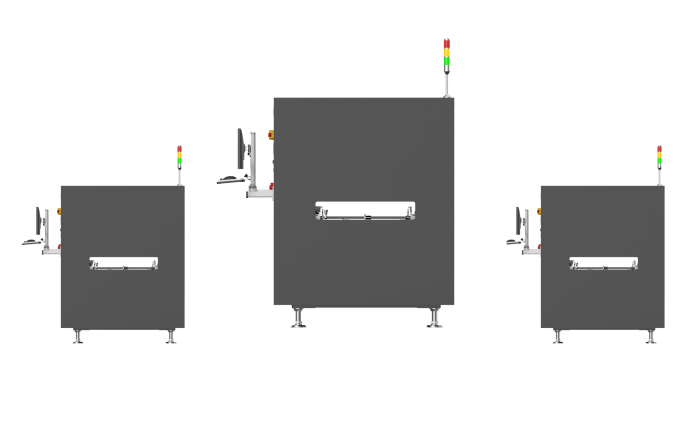

Diese CSPs stellen für die Hersteller von Anlagen zur Kapselung von Chips einen Wachstumsmarkt dar, doch die Entwicklung von Geräten, die zur Verarbeitung von Chips benötigt werden, ist alles andere als einfach. Solche Geräte müssen nicht nur präzise und zuverlässig arbeiten, sondern auch noch kosteneffektiv sein und einen hohen Durchsatz ermöglichen. Hinzu kommt, daß die Montage von Subsystemen immer häufiger von Montage-Dienstleistern übernommen wird. Die Gründe sind offensichtlich: Zum einen verringern sich dadurch die Kapitalaufwendungen und die Gesamtkosten, und zum anderen können sich die Hersteller integrierter Geräte (Integrated Device Manufacturers, IDMs) auf ihre eigenen Kernkompetenzen konzentrieren. Deshalb nehmen mehr und mehr IDMs die Dienste von Montagebetrieben in Anspruch, um kundenspezifische Lösungen zu realisieren. Daraus folgt, daß die Montagebetriebe in der Lage sein müssen, Gehäuse in den unterschiedlichsten Technologien zu liefern. Das wiederum stellt erhöhte Anforderungen an die Produktionsanlagen, die eine Verarbeitung von Gehäusen neuester Technologie gestatten und ohne größeren Aufwand an unterschiedliche Montagetechniken anpassbar sein müssen: Damit sind die Anforderungen an die Herstellung von Geräten zur Fertigung von Unterbaugruppen so anspruchsvoll wie nie zuvor.

Chipmontage: Herausforderung in der Gehäuseverarbeitung

Ein wesentlicher Schritt für die Beherrschung der Gehäusetechnologien ist die Montage oder das Bonden des Chips auf dem Gehäusesubstrat. Je nach gewählter Verbindungstechnik zwischen Chip und Substrat mit der Chipstruktur nach oben und darauffolgendem Drahtbonden, oder mit der Chipstruktur nach unten, dem sogenannten Flip-Chip-Bonden. Das zur Chipmontage eingesetzte Verfahren hat großen Einfluß auf die Ausbeute der nachfolgenden Prozesse und die Zuverlässigkeit der Gehäuse.

Die CSPs verlangen den Anlagen zur Chipmontage neue Fähigkeiten ab. Da sowohl Chips, als auch gewünschtes Gehäuseformat (nur 20% größer als der Chip selbst) dramatisch kleiner geworden sind und die Zahl der Ein- und Ausgangspins pro Chip zugenommen hat, ist die präzise Montage des Chips auf dem Gehäusesubstrat zu einer echten Herausforderung geworden. Anlagen zur Chipmontage sollten die Möglichkeit zur automatisierten und präzisen Positionierung des Chips bieten, einen hohen Durchsatz erzielen und dennoch zu niedrigen Preisen zu haben sein. Überdies nimmt auch der Bedarf an der Montage von Multichipmodulen (MCMs) bzw. System-in-Package-Anwendungen (SiP) rapide zu. Es müssen also neue und hochgradig flexible Chipmontage-Maschinen entwickelt werden, damit die Entwicklung immer komplexerer Gehäuse weitergehen kann.

Extrem enge Toleranzen

Ein wichtiger Parameter, ausschlaggebend für die elektrischen und thermischen Eigenschaften des Endproduktes, ist die Kleberschichtdicke (Bond Line Thickness, BLT). Die BLT ist der Abstand zwischen der Unterseite eines gebondeten Chips und der Oberseite des Substrats. Die Fortschritte in der Montagetechnik hin zu immer komplexeren Gehäusen haben zunehmenden Einfluß auf die zulässigen Toleranzen für die BLT und die Chipneigung (Planparallelität zwischen Chip und Substrat). Das führt zu immer extremeren Toleranzvorgaben, die dann in der Chipmontage als normal betrachtet werden. Als Lösung für ICs mit hoher Pinzahl werden heute gemeinhin Ball-Grid-Arrays (BGAs) verwendet. BGA-Streifen zeigen aber sehr häufig beträchtliche örtliche und durchgehende Verformungen und Dickenschwankungen, und die Maßtoleranzen können sich leicht auf das Zehnfache der Werte summieren, diefür herkömmliche Metallanschlussrahmen (leadframes) bekannt sind.

Auch die Dickenschwankungen müssen berücksichtigt werden. So kann die Chipdicke auf ein und demselben Wafer um ± 2,5 µm oder mehr variieren. Schwankungen zwischen unterschiedlichen Wafern können noch erheblich größer sein und durchaus ± 25 µm oder sogar mehr betragen.

Dies zeigt, daß die Einhaltung immer enger werdender Toleranzvorgaben bei der Chipmontage einer Reihe von Faktoren unterliegt, so z.B. der Substratdicke, der Verformungen des Substrats, der Chipdicke und der Chipneigung. Um nun zu vermeiden, daß dieser Schritt der Chip-Positionierung in der Verarbeitung zu einem Qualitäts-Engpaß wird, sollten Maschinen zur Chipmontage so ausgelegt sein, daß sie diese engen Toleranzen einhalten.

In einigen Anwendungsfällen, beispielsweise bei Leistungsverstärkern für Geräte der Mobilkommunikation, hat die BLT großen Einfluß auf die elektrischen und thermischen Eigenschaften der Elemente. So bestimmt die BLT die Zuverlässigkeit und mithin die Qualität der Verstärkerkomponente ganz wesentlich.

Das Positionieren eines Chips auf einem gewellten Substrat kann eine knifflige Angelegenheit sein. Konventionelle Werkzeuge zur Chippositionierung können, wenn sie in Verbindung mit erheblich verformten Substraten eingesetzt werden, ungleichmäßige BLT-Werte zur Folge haben, die nicht innerhalb der Toleranzvorgaben liegen. Solche Verformungen können beispielsweise beim Aushärten des Epoxidharzes während der Oberflächenmontage entstehen und durch Widerstände oder Kondensatoren in der Nähe der Chip-Position verursacht werden. Wellverformungen in der Größenordnung von 100 µm oder mehr sind durchaus nichts Ungewöhnliches. Dieses Problem ist in der Regel mit mechanischen Mitteln nicht zu lösen, allenfalls durch die Anwendung von speziell dafür vorgesehenen Maskenlösungen, die sich aber von einem Anwendungsfall zum anderen unterscheiden und zudem die Kosten in die Höhe treiben. Umgehen könnte man dieses Problem, indem man die SMD-Aushärtephase vor der Chip-Positionierung durchführt, was aber mit höheren Betriebstemperaturen verbunden ist.

Eine Möglichkeit zur Lösung dieser Probleme besteht darin, ein Werkzeug zu verwenden, das speziell für das Arbeiten mit extrem geringen Bondkräften ausgelegt ist, so z.B. das zum Patent angemeldete neue Ultra Light Tool (ULT) von Datacon. Beim ULT sind die Bondkräfte auf 0 bis 6 g begrenzt. In diesem Bereich ist die Abhängigkeit der Bondkraft von der aktuellen Höhenposition oder Verformung sehr gering. Das bedeutet, daß Wellverformungen (Höhenschwankungen) des Substrates von 100 bis 200 µm nur einen sehr geringen Einfluß auf die vom Bondwerkzeug ausgeübte Kraft haben und damit trotz Welligkeit des Substrates eine Konstanz der Kleberschichtdicke in der Größenordnung von w15 µm zwischen Substrat und Chip erreicht werden kann. Auch bei der Verarbeitung von gewellten Substraten in Kombination mit Epoxy niedriger Viskosität liefert das ULT beeindruckende Ergebnisse. Ein weiterer Vorteil des ULT zeigte sich bei der Herstellung von CSPs-Packages oder Chip-Stapel-Anwendungen (stacked die applications) mit sehr engen Toleranzen bezüglich der Kleberausbreitung am Chiprand. Einerseits muss eine 100%ige Benetzung der Chipunterseite mit Kleber sichergestellt sein, andererseits soll der Kleber aufgrund der immer enger werdenden Gehäuseabmessungen so wenig wie möglich über den Chiprand hinauslaufen. Hierbei hat die Verwendung des Datacon Ultralight Tools ebenfalls gute Ergebnisse erbracht.

Die heutigen Werkzeuge für die Chipmontage, einen vielleicht häufig vernachlässigten Schritt in der Fertigung von Halbleiterbauelementen, sollten die erforderlichen engen Toleranzen bewältigen, die durch die immer kleineren und komplexeren Gehäuse eingehalten werden müssen. Gebraucht werden heute sehr flexible Chipmontage-Maschinen, die in der Lage sind, unter Einhaltung aller qualitätsrelevanten Parametertoleranzen (z.B. Kleberschichtdicke) den Chip präzise zu positionieren und gleichzeitig einen hohen Durchsatz zu erzielen, damit vermieden wird, daß die Chipmontage in der Halbleiter-Fertigungsindustrie zu einem Engpaß wird.

EPP 185

Unsere Webinar-Empfehlung

10.10.22 | 10:00 Uhr | Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine…

Teilen: