Teradyne’s Integra division has intro-duced the J750k test system with a very low entry-level price for low-end semiconductors. It was designed specifically to reduce the cost of test without compromising production efficiency, flexibility or reliability. The basic configuration starts with 64 pins at 33MHz, andcan be expanded to up to 256 pins/66MHz or to a 512 pin configuration. As requirements increase, the system may be upgraded to higher pin counts and speed with field hardware and software upgrades. The instrument may also be configured with options such as for mixed-signal or memory test. According to the supplier, the J750k delivers the lowest priced leading-edge ATE technology on the market, and is compatible with the entire family. It achieves over 95% parallel test efficiency and its zero footprint design allows for efficient use of production floor space toreduce cost of ownership. Thesystem also features IG-XL software, the industry’s first test development suite combining the power and performance of the latest PC technology and Windows NT operating system with the familiarity of standard Windows productivity tools, like Microsoft Excel and Visual Basic.

EPP 224

Unsere Webinar-Empfehlung

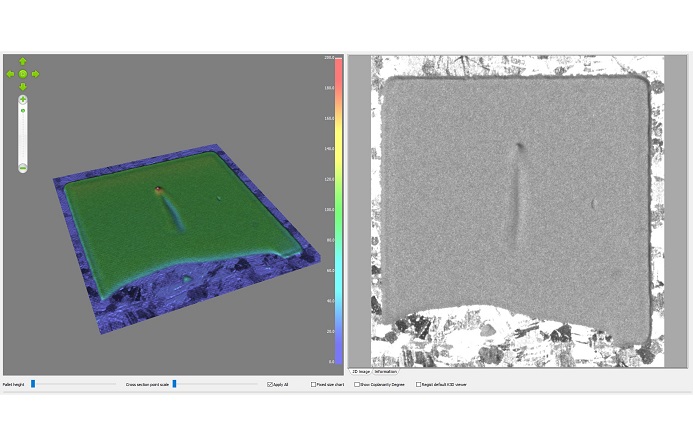

Applikationen aus dem Bereich der Leistungselektronik gewinnen immer mehr an Bedeutung. Die Inspektion dieser Applikation lässt sich mit der bewährten Standardtechnologie der 3D-Messtechnik bewerkstelligen.

Teilen: