CoreCommander von JTAG Technologies ist ein einfaches Low-Cost-System, das Kern-Emulationsmodi von Mikroprozessoren für die Hardware-Validierung und den Baugruppentest nutzt. Über die einfach zu verwendende Benutzerschnittstelle und die Low-Cost Interface-Hardware kann der Anwender in kürzester Zeit aus dem Prozessorkern heraus Lese- und Schreibsequenzen an eingebettete oder externe Peripherie und Peripherie-Controller entwerfen. Der Support für Python ermöglicht es dem Anwender darüber hinaus, über die benutzerfreundliche Live-Umgebung ausgefeiltere Testsequenzen unter Benutzung der CoreCommander-Pythonbibliotheken zu gestalten. Zu den unterstützten Kernarchitekturen zählen ARM 7/9/11, Cortex, Marvells PXA, Microchips PIC32, TIs C2000, Freescales PowerPC/Nexus und Infineons TriCore.

CoreCommander bietet zwei Betriebsmodi:

- Interaktiver Modus: direkte Kontrolle der Core

- „Python embedded“ Modus: Die Kontrolle der Core kann per Scripting in ein vollständiges Testprogramm eingebunden werden.

Dieses Produkt beinhaltet automatisch das kostenloses Softwaremodul JTAG Live Buzz.

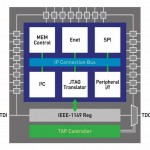

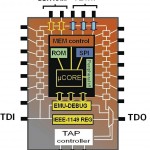

Die JTAG-Steuerung von Mikroprozessoren und DSPs erfolgt über den Zugriff auf die Core über die Debugschnittstelle und bietet

- Unterstützung der gängigsten Kerne

- Erstellung von Cluster-Tests und Flash-Anwendungen

JTAG Live Studio ist das umfassende Paket von JTAG/Boundary-Scan-Werkzeugen, das es Entwicklern und Produktionstest-Ingenieuren gleichermaßen ermöglicht, vollständige Test- und Programmieranwendungen zu entwickeln – zu einem bisher unerreicht niedrigen Preis. Auch Designs mit nur wenigen, sogar nur einem oder zwei, JTAG-Bauteilen können in allen Stufen des Lebenszyklus in hohem Maß von dieser Technologie profitieren. Die Lösung begründet eine neue Klasse von Werkzeugsätzen für Bauteil-Programmierung und Test, das die Einstiegskosten für Test- und Hardwareingenieure drastisch senkt und trotzdem sowohl die zahlreichen herkömmlichen Vorteile von JTAG/ als auch neuere Technologien wie prozessorgesteuerte Tests bietet. Es arbeitet sowohl mit als auch ohne Netzlistendaten des Designs und kann für Verbindungstests (einzelne Netze bis zu kompletten Leiterplatten), Logik-Clustertests, Speichertests und andere eingesetzt werden. Studio umfasst auch Möglichkeiten zur Bauteilprogrammierung, die die Datenformate JAM/STAPL und SVF für die Programmierung der Konfigurations-PROMs von CPLDs und FPGAs unterstützen. Auch Flash-Speicher und serielle PROMs lassen sich problemlos programmieren. Low-cost-Optionen für den Zugriff auf Debug-Modi von Prozessorkernen ermöglichen einen kostengünstigen Zugang zu Testverfahren, die verschiedentlich unter den Bezeichnungen „Processor Controlled Test“ und „JTAG Emulation Test“ bekannt sind.

Unsere Webinar-Empfehlung

Die Zuhörer erhalten Informationen zur Effizienzsteigerung von AOI-Systemen bei Nutzung von Digitalen Zwillingen von der zu prüfende Baugruppe bzw. des eingesetzten Inspektionssystems.

Teilen: