Entwickler und Designer von Hochfrequenzschaltungen wissen, dass sie die Impedanz von Leiterbahnen errechnen und beim Erstellen des CAD-Layouts beachten müssen. Weniger geläufig dagegen ist, dass auch für viele „normale“ Digitalschaltungen die Impedanz der Signalleiterbahnen und der Stromversorgung zunehmend eine funktionsentscheidende Rolle spielt. Die Ursache ist in den kürzer werdenden Schaltzeiten moderner Bauelemente zu suchen. Die Elektronikindustrie steht folglich vor der Aufgabe, sich verstärkt mit dem Einsatz impedanzkontrollierter Leiterplatten auseinanderzusetzen. Dieser Beitrag gibt einen Einblick in die Klassifizierung der Impedanzen und wendet sich dann der asymmetrischen Single-Stripline zu.

Arnold Wiemers, ILFA, Hannover

Obwohl für viele industrielle Anwendungen nicht unbedingt erforderlich, rücken die Taktraten auf den Signalleitungen in den 100-MHz-Bereich und die der Chips in den Gigahertz-Bereich vor. Die Schaltzeiten der assoziierten Chips fallen auf ein bis zwei Nanosekunden oder sogar darunter. Im Endeffekt entstehen High-Speed-Schaltungen, für die physikalische Be-dingungen berücksichtigt werden müssen, die bisher außer Acht gelassen werden konnten.

Für die zuverlässige Funktion der zukünftigen Baugruppen müssen elementare Designregeln beachtet werden. Ganzflächige Powerplanes, die eine Breitbandentkopplung durch kapazitive Eigenschaften bieten, gehören dazu. Ebenfalls strikte Routingstrategien, die Schlitzantennen vermeiden und für eine optimale Signalrückführung sorgen (Schlitzantennen können hochfrequente Störabstrahlung von den Planes auslösen). Das Schaltungskonzept und die Auswahl der Bauteile müssen die Signalführung in einem homogenen elektrischen Feld mit Hilfe impedanzkontrollierter Leitungen gewährleisten.

Eine Voraussetzung für das Lösen dieser Aufgabe ist das Umsetzen dieser technischen Anforderungen auf der Leiterplatte, die damit als Träger der Baugruppe eine funktionsentscheidende Rolle bekommt. Es besteht kein Grund zur Annahme, dass die Leiterplatte die geforderten Ansprüche nicht erfüllen könnte, aber CAD-Designer und Leiterplattenhersteller müssen sich über die Vorgaben und Einflüsse der Herstellungstechnik bewusst sein. Ihnen müssen auch die wichtigsten Parameter bekannt sein, die die Impedanz einer Signalleitung bestimmen.

Impedanzen: Begriffe und Geometrien

Die Impedanz einer Signalleitung hängt von zwei Parametern ab:

• der Impedanzklasse und dem Impedanztyp sowie

• dem geometrischen Leiterplattenaufbau.

Es gibt vier Impedanzklassen: Die Single-Ended-Impedanz ergibt sich durch die Referenz einer einzelnen Leiterbahn zu einer oder zwei Powerplanes. Die differentielle Impedanz ergibt sich durch zusammengehörige inverse Signale in zwei parallel verlaufenden Leiterbahnen, die in Referenz zu einer oder zwei Powerplanes stehen können. Die koplanare Impedanz entsteht durch eine Signalleiterbahn, die in Potentialleiterbahnen oder in Potentialflächen eingebettet ist. Signal und Potential können in Referenz zu einer oder zu zwei Powerplanes stehen. Die differentiell-koplanare Impedanz schließlich ergibt sich durch zusammengehörige inverse Signale in zwei parallel verlaufenden Leiterbahnen, die in Potentialflächen eingebettet sind, mit Referenz zu einer oder zwei Powerplanes.

Allgemein werden alle Impedanzvarianten nochmals danach unterschieden, ob die Signalleiterbahn zwischen zwei Powerplanes liegt (Stripline) oder über einer Powerplane ohne weitere planare Abdeckung nach außen (Microstrip). Für jede dieser Impedanzklassen gibt es mehrere geometrische Lösungen auf der Leiterplatte, die üblicherweise als Multilayer aufgebaut ist. Entsprechend der geometrischen Aufbauvariante werden die Impedanztypen weiter unterteilt, wie die Beispiele für die Single-ended-Impedanzen in den Bildern 1 bis 6 zeigen.

Asymmetrische Single-Stripline-Impedanz

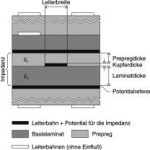

Die Impedanz dieses Aufbaus ergibt sich durch das elektromagnetische Feld, das sich zwischen der Leiterbahn und den beiden sie abdeckenden Powerplanes ergibt. Aus Sicht der Leiterplattentechnik ist zu bemerken, dass die Impedanz ausschließlich von mechanischen Bedingungen abhängig ist, nämlich von der Breite der Leiterbahnen und von den Lagenabständen; das ist in der Praxis die Dicke der Laminate und Prepregs. Als weiterer Parameter ist die dielektrische Eigenschaft (er-Wert) des eingesetzten Materials vorgegeben (Bild 7).

Sind die Abstände der Ebenen im Multilayer und der er-Wert des Materials bekannt, dann ist es problemlos möglich, die resultierende Impedanz für eine vorgegebene Leiterbahnbreite und für eine vorgegebene Leiterbahndicke (das heißt die Kupferdicke des Materials) mit einem Softwareprogramm zu berechnen. Leider führt diese Kalkulation einer Impedanz in der Praxis nicht zum gewünschten Ergebnis. Es soll ja nicht ermittelt werden, welche Impedanz ein Multilayeraufbau ergibt, sondern es ist umgekehrt der erforderliche Impedanzwert vorgegeben und es soll errechnet werden, welcher Multilayeraufbau diese gewünschte Impedanz haben wird.

Üblicherweise liegen erstrebenswerte Impedanzen für homogene Leiterbahnsysteme bei 50, 75 oder 100 q. Um ein solches Ergebnis zu erhalten, können die Lagenabstände, die Leiterbahnbreite, die Leiterbahndicke und natürlich auch der er-Wert verändert werden. Mit üblichen Softwareprogrammen wird durch die Vielzahl der änderbaren Parameter die Berechnung deshalb zu einem langwierigen Spiel von Versuch und Irrtum.

Ist endlich der erwünschte Wert errechnet, stellt sich das nächste Problem. Es muss dann gewährleistet sein, dass die Materialdicken auch wirklich als Innenlagenlaminat zur Verfügung stehen oder aus Prepregs aufgebaut werden können. Da grundsätzlich die Kosten für die Baugruppe zu berücksichtigen sind, muss zudem beachtet werden, ob die Materialien zu vertretbaren Preisen verfügbar sind und ob die Fertigung der Leiterplatten mit herkömmlichen Verfahren möglich ist.

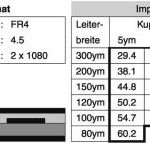

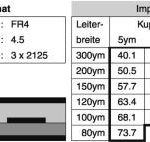

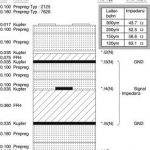

Man geht deshalb den umgekehrten Weg, indem zu den vorhandenen üblichen Produktionsprozessen und zu den möglichen und üblichen Materialkombinationen in einem Multilayer die Impedanzen bereits berechnet und tabellarisch dargestellt worden sind (Bilder 8 und 9). Die Tabellen unterscheiden verschiedene Leiterbahnbreiten, so wie sie heute meistens eingesetzt werden, und die üblichen Kupferdicken, die ja identisch mit der Leiterbahnhöhe sind. Es sind bereits die aktuellen Grenzbereiche zu HDI (High-Density-Interconnection) berücksichtigt, die pauschal bei Bahnbreiten von 150 µm beginnen, sowie die MFT (Micro-Fineline-Technology), die Bahnbreiten unter 100 µm und schmaler definieren. Aus verfahrenstechnischen Gründen sind die anspruchsvolleren Bereiche der HDI (und MFT) in der bisher gängigen Kupferdicke von 35 µm nicht mehr herstellbar. Diese Leiterbilder werden mit Kupferdicken von 17, 9 oder 5 µm strukturiert, sodass für diese Dicken ebenfalls gerechnet wurde.

Für alle Impedanzberechnungen wurde erst einmal von idealen Bedingungen ausgegangen, das heißt, Dickentoleranzen der Materialien und Dickenänderungen während des Pressvorgangs in der Produktion sowie Veränderungen der Querschnittsgeometrie der Leiterbahnen durch die Rückätzung wurden nicht mit ins Kalkül gezogen.

Aus der Analyse der Tabelle in Bild 8 ergeben sich dann folgende Ergebnisse. Erst einmal ist dieser Aufbau als Teil eines Multilayers herstellbar, weil das eingesetzte 200-µm-Laminat zu normalen Kosten verfügbar ist. Gleiches gilt für die beiden Prepregs vom Typ 1080 (60 µm dick). Beide Komponenten sind aus Standard-FR4 und mit handelsüblichen Kupferdicken beschichtet. Weiter lässt sich aus der Tabelle ablesen, welche Tendenz der Impedanzwert hat, wenn die Leiterbahnbreite verringert wird (das heißt, die Impedanz nimmt zu) oder wenn die Kupferdicke vergrößert wird (das heißt, die Impedanz nimmt ab). Zudem ist zu erkennen, in welchem Maß die Veränderungen stattfinden, also ob die Impedanz drastisch oder eher moderat zunimmt.

Als nächstes ist aus der Tabelle zu erkennen, ob mit dieser Materialkombination bei entsprechender Wahl von Leiterbahnbreite und Kupferdicke der gewünschte Widerstandswert für die Impedanz überhaupt realisierbar ist. Es ist schnell ersichtlich, dass 100 oder 75 q nicht erreicht werden. Mit 50,2 q findet sich ein recht gut passender Wert für eine Kupferdicke von 5 µm, aber erst bei einer Leiterbahnbreite von 120 µm. Die 5 µm Kupferdicke wären für kurze Signalleitungen im Prinzip eine denkbare Lösung (bei längeren Signalleitungen wäre schon wieder der steigende ohmsche Widerstand zu berücksichtigen). In der Kalkulation der Kosten für die Fertigung der Leiterplatte wird diese Bahnbreite von 120 µm jedoch von Seiten der Leiterplattenhersteller bezuschlagt. Die Entscheidung für die Verwirklichung einer Impedanz mit 120 µm breiten Signalbahnen würde deshalb die Leiterplatte deutlich verteuern. Ein höchst unerfreulicher Effekt, wenn ansonsten das Layout diese minimale Bahnbreite für die Entflechtung nicht erforderlich macht.

Praxisgerechtere Resultate ergeben sich da schon aus der Tabelle in Bild 9, aus der herausgelesen werden kann, dass sich mit 48,1 q schon eine gute Näherung bei einer Standardkonfiguration mit 17 µm Kupfer und mit einer 200 µm breiten Leiterbahn ergibt. Das Abschätzen einer Bahnbreite von 150 µm mit 54,7 q ergibt, dass mit Anpassen der Leiterbahnbreite auf 180 µm eine Impedanz von zirka 50 bis 51 q erreicht werden müsste.

Diese Betrachtung ist nicht ganz korrekt, weil hinter den Impedanzberechnungen mathematische Modelle mit logarithmischen Funktionen stehen. Die Abschätzung ist aber in der Praxis tauglich, weil für den Im-pedanz-Zielwert in der Regel eine Abweichung von ± 10% zulässig ist, ohne dass die spätere Funktion der Baugruppe dadurch normalerweise beeinträchtigt wird. Soll dennoch der Wert für die Leiterbahnbreite präzise ermittelt werden, dann wäre mit den Parametern für Bahnbreite und Kupferdicke eine Startvorgabe für ein Softwareprogramm gegeben und aus der Tabelle würde sich ergeben, dass der Parameter für die Leiterbahnbreite von 200 µm in Richtung 180 µm verändert werden müsste, bis das geforderte Ergebnis exakt vorliegt.

Es sei bei dieser Gelegenheit erwähnt, dass die Kupferdicke natürlich nicht verändert werden darf. Die Abschätzung über die Tabelle zeigt, dass eine Kupferdicke von zirka 7 µm auch eine Lösung sein könnte, nur gibt es in der Praxis kein Innenlagenlaminat mit dieser Kupferdicke. Dem Layouter bleibt also nur die Korrektur der Impedanz durch die Einstellung der richtigen Leiterbahnbreite, aber auch dabei ist zu beachten, dass ein virtueller Idealwert von beispielsweise 181,5 µm in der Leiterplattenproduktion illusorisch ist.

Ist für die Impedanz die Variante „Single Stripline asymmetrisch“ ermittelt, dann bleibt die Aufgabe, das so erhaltene „Impedanzmodul“ in den Aufbau eines Multilayers zu integrieren. Wie die geometrische Verteilung der Layoutlagen in einem Multilayersystem mit sechs Lagen aussehen könnte, ist in Bild 10 gezeigt. Bei der Layoutarbeit müsste beachtet werden, dass die mit der erforderlichen Impedanz behafteten Signale in Lage „I4“ gelegt werden. Die Lagen „I3“ und „I5“ müssen dann ein Potential führen, entweder 2 x GND, 2 x VCC oder GND und VCC. In diesem Beispiel ist für die Lagen „I3“ und „I5“ GND vergeben.

Für die Impedanz sind die verbleibenden drei Lagen („BS“, „I2“ und „LS“) ohne Einfluss. Sie könnten je nach Erfordernis vergeben werden. Liegen beispielsweise für die Schaltung zusätzlich EMV-Anforderungen vor, dann könnte Lage 2 mit VCC belegt werden, was eine unterstützende Breitbandentkopplung für die Schaltungsfunktion ergeben würde. Die Außenlagen BS und LS wären dann noch frei für Signalleiterbahnen und natürlich für die Anschlusspads von SMT-Bauteilen.

Dem versierten Layouter fällt sicher auf, dass dann im Endergebnis eine GND-Lage zusätzlich eingefügt ist, die nicht unbedingt erforderlich ist und die den hart umkämpften Raum für die Entflechtung der Schaltung im Layout reduziert. Dieser Effekt ist bei impedanzkontrollierten Schaltungen typisch. Es müssen oft zusätzliche Lagen eingebaut werden, insbesondere wenn mehrere Ebenen eines Multilayers impedanzkontrolliert sind, um die Aufgabenstellungen zu lösen. Dies ist mit ein Grund für die Prognose, dass die Lagenanzahl von Multilayern auch für Standardanwendungen zukünftig zunehmen wird und dass üblicherweise Multilayer mit acht und zehn Lagen zu erwarten sein werden.

Obwohl sich impedanzkontrollierte Multilayer relativ einfach aufbauen lassen, müssen sie nach Fertigstellung geprüft werden. Die Prüfung der Impedanz der Leiterplatte ist meistens aufwändig und mit einfachen Mitteln nicht durchführbar. Erst die Fehlfunktion der bestückten Baugruppe legt die Vermutung nahe, dass die vorgesehene Impedanz in der Fertigung der Leiterplatte möglicherweise nicht erreicht wurde. Diese Erkenntnis ist zu diesem Zeitpunkt fatal, weil die Baugruppe damit unbrauchbar und der wirtschaftliche Schaden groß ist. Es ist daher erforderlich, die Leiterplatten bereits im Haus des Herstellers auf ihre ordnungsgemäße Funktion zu prüfen.

Unsere Webinar-Empfehlung

10.10.22 | 10:00 Uhr | Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine…

Teilen: