Boundary Scan gewinnt rasant als ergänzendes Testverfahren in der Prüfung von elektronischen Baugruppen an Bedeutung. Dort, wo Testverfahren wie der Incircuit-Test und der Funktionstest in Sachen Kontaktierbarkeit bzw. Fehlerdiagnose limitiert sind, kann Boundary Scan als komplementäres Verfahren zur Lösung beitragen. In dem Artikel werden die Möglichkeiten und die Implementierung von Boundary Scan in den Produktionstest, am Beispiel der Testlösung Diatem aufgezeigt.

Tecs Prüftechnik, Furtwangen & Temento Systems, Berlin

In der zweiten Hälfte der 80iger Jahre entwickelte eine Gruppe von visionären Testingenieuren die Boundary-Scan-Technologie. Anspruch dieser Entwicklung war es, für nicht oder nur aufwändig kontaktierbare elektrische Knoten trotzdem einen Zugriff zu ermöglichen. Die Kontaktiermöglichkeit sollte insbesondere dann ermöglicht werden, wenn neue Gehäusebauformen bzw. Platzverhältnisse einen physischen Zugriff mittels Testadapter eingeschränkt oder gar unmöglich machen. Die genannte Entwicklungsgruppe, bekannt als Joint Test Action Group (JTAG), führte ihre Arbeiten schließlich konsequent zur Standardisierung nach IEEE.

Unter der Bezeichnung IEEE1149.1 ist als Norm spezifiziert, wie digitale ICs im Einzelnen aufzubauen sind. Neben der eigentlichen Kernlogik eines ICs (z.B. das Gatter-Array eines FPGAs) gehören dann auch für jeden Pin eine JTAG-Scan-Zelle sowie, zur internen Ablaufsteuerung dieser Zellen ein TAP-Controller zur Schaltung. Dabei sind die JTAG-Scan-Zellen innerhalb als Schieberegister miteinander verbunden. Durch entsprechende an den TAP-Controller gegebene Befehle, wird die Kernlogik des ICs für die Zeit des Testens von dem Kontakt zu den Pins abgetrennt, und es können in diesem Zustand Signalwerte für HIGH bzw. LOW über die JTAG-Scan-Zellen gelesen oder geschrieben werden. Das Einlesen der Werte IN bzw. das Auslesen der Werte AUS der Komponente erfolgt seriell über die JTAG-Scan-Zellen. Somit werden die Signalwerte per Schieberegister transferiert. Jeder JTAG-fähige IC hat Pins mit den Bezeichnungen:

TCK … Testclock

TMS … Test Mode Select

TDI … Test Daten In

TDO … Test Daten Out

TRST … Test Reset (optional).

Werden die auf einem Board vorhandenen JTAG-fähigen ICs über einen externen BUS seriell (TDO => TDI => TDO) und parallel (TCK, TMS, TRST) miteinander verbunden, so ist die Signalbeobachtung nicht mehr nur an der Komponente, sondern jetzt auch auf Board-Ebene möglich. Der Schaltplan bestimmt, in welche Netze die Pins der JTAG-ICs in der jeweiligen Version „hineinreichen“, wo also überall Werte gelesen bzw. geschrieben werden können. Im Ergebnis des Tests gibt es Aussagen darüber, ob und wo genau Bestück- bzw. Lötfehler vorliegen.

Anforderungen an den Produktionstest

Drei Hauptziele für den Produktionstest lassen sich ganz allgemein formulieren:

- Erreichen einer hohen Testabdeckung, für die Sicherstellung einer hohen Produktqualität

- Schnelles Testen, für einen raschen Markteintritt des Produktes

- Niedrigste Kosten, durch rasche Erstellung von Tests auch für komplexe Produkte, durch Automatisierung von Prozessen und Nutzung von Standardlösungen.

Angesichts stetig steigender technologischer Anforderungen, wie BGA-Gehäusebauformen, Anzahl Pins pro Bauelement, Anzahl der Board Layer, höhere Signalgeschwindigkeiten, allgemeine Miniaturisierung, sind die o.g. Hauptziele zunehmend schwerer miteinander zu vereinbaren.

Schneller am Markt sein zu wollen oder zu müssen, erhöht den Druck auf den Produktentstehungszyklus. Diesen abzukürzen geht nicht selten zu Lasten der zur Verfügung stehenden Zeiten im Testbereich. Eine eher kritisch zu sehende Konsequenz angesichts dessen, dass jede neue µP Generation im Vergleich zur vorangegangenen den Testaufwand etwa verdoppelt.

Und mit Blick auf die Testkosten, welche selbst typisch bis zu 30% der gesamten Herstellungskosten des Produktes betragen, liegen die Prioritäten klar auf der Hand: Es gilt, der Fertigung Testtechniken zur Verfügung zu stellen, die einerseits erforderliche Zeiten und Kosten reduzieren, und andererseits auch bei stetig steigenden technologischen Anforderungen die Produktqualität sichern.

Teststrategie

Entscheidend ist es, nach gründlicher Projektanalyse eine Teststrategie zu entwerfen, die die möglichen Testverfahren so kombiniert, dass maxímale Qualität bei minimalen Testkosten zustande kommt. Die Nachteile eines Verfahrens werden dabei durch die Vorteile des anderen, komplementären Verfahrens wettgemacht. Zur Verfügung stehen dafür heute sowohl optische als auch elektrische Testverfahren. Eine beispielhafte Einordnung der Verfahren zeigt Bild 1, wobei Boundary Scan klar zur Gruppe der elektrischen Testverfahren gehört.

Betrachtungen zu den Testverfahren

Die Automatische Optische Inspektion (AOI) kann sehr flexibel an verschiedenen Abschnitten der Produktion eingesetzt werden (z.B. nach Lotpastendruck, Bestückung und Löten). AOI ersetzt heute in vielen Bereichen die sonst übliche Sichtprüfung.

Der Incircuit-Test (ICT) ist wegen den Adaptionskosten insbesondere für mittlere bis große Produktionsvolumina wirtschaftlich. Für jedes neue Projekt muss ein Nadelbettadapter erstellt werden, was deutlich auf der Kostenseite zu Buche schlägt.

Der Flying-Probe-Tester (FP) macht einen reinen analogen Incircuit-Test, d.h. digitale ICs werden nicht getestet, Lötstellen an ICs können jedoch gegebenenfalls mittels vektorlosen Testverfahren überprüft werden. Der Flying-Probe-Tester kommt allerdings ohne Nadelbettadapter aus, da die Kontaktierung über fliegende Finger erfolgt. Er ist damit flexibler als der ICT und wird vorteilhaft bei kleinen Produktionsvolumen eingesetzt.

Der Funktionstest (FT) gibt eine JA/NEIN Aussage darüber, ob das Board seine Funktion erfüllt. Im Fall von NEIN (Prüffehler), steht somit nur fest, dass das Board fehlerhaft ist, nicht aber WO der Fehler zu finden ist bzw. WAS für ein Fehler aufgetreten ist.

Fazit

Im Vergleich der elektrischen Testverfahren untereinander fällt auf, dass sowohl ICT als auch FP in Sachen Kontaktierbarkeit (zunehmend) limitiert sind. Schätzungen sprechen davon, dass die Abdeckung der Testknoten mit ICT und FP von derzeit ca. 50% auf ca. 10% im Jahr 2010 sinken wird. Beim Funktionstest wird mit steigender Komplexität der Baugruppen die Fehlerdiagnose immer schwieriger bis praktisch unmöglich.

Boundary Scan ist komplementär – Vorteile beim Einsatz im Prüffeld

Dass Boundary Scan als elektrisches Testverfahren auf den ersten Blick gut zu optischen Verfahren passt, liegt auf der Hand. Der vorteilhafte und komplementäre Charakter des Verfahrens auf elektrischer Ebene wird aber vor allem bei zusammenhängender Betrachtung mit FP, ICT und FT deutlich.

Am konkreten Beispiel des Boundary-Scan-Testsystems Diatem (Temento Systems, France) soll nachfolgend die Arbeitsweise veranschaulicht und wichtige Ergebnisfenster vorgestellt werden.

Boundary Scan liefert bereits früh erste Ergebnisse, und zwar bereits beginnend in der Phase der Schaltungsentwicklung und konkret in Form eines Analysereports zur Testabdeckung.

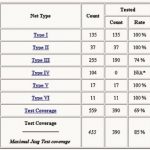

Im Beispiel in Bild 2 hat die Analyse ergeben, dass 455 von insgesamt 559 Netzen mittels Boundary Scan erreichbar sind. Dies entspricht einer maximalen Testabdeckung von 455/559 => 81%. Die durch das Testfile aktuell erreichte Anzahl der Netze beträgt absolut 390. Das sind 69% Gesamttestabdeckung über alle Netze, und 85% bezogen auf die erreichbaren JTAG-Netze. Durch weitere Optimierung sind also noch 15% Steigerung möglich.

Im Ergebnis des Reports können die Testingenieure somit sehr frühzeitig feststellen, welche Reichweite die “virtuellen Nadeln“ von Boundary Scan in der Applikation tatsächlich haben werden, und welche Bereiche durch andere elektrische Testverfahren noch abzudecken sind.

An dieser Stelle sei betont, dass Boundary Scan seit der Einführung der Technologie seinen Leistungsbereich deutlich erweitert hat. Entgegen sich stellenweise noch hartnäckig haltenden Meinungen, können mit Boundary Scan dank Cluster-Methoden hohe Testabdeckungen auch mit wenigen JTAG-ICs erreicht werden. So gesehen, kann BoundaryScan bereits ab ein JTAG IC sinnvoll sein [1,2].

Wurde die Analyse erfolgreich erstellt, so liegt im Prinzip der komplette Boundary-Scan-Prüfplan für den Test in der Produktion bereits vor. Sowohl Prototypen als auch Serientests können somit unmittelbar und ohne Zeitverzug vorgenommen werden.

Im Fehlerfall liefert das System einen interaktiven Testreport, in welchem der Anwender eine präzise Aussage darüber erhält, welche Fehler, geordnet nach Kategorie, wo genau aufgetreten sind. Im Beispiel in Bild 3 wurde ein GND-Fehler ermittelt. Das Netz „Proto2_IO28“ ist betroffen. Um nun schnell Details einsehen zu können, wird über Klick auf das betroffene Netz der Netznavigator aufgerufen.

Im Netznavigator, in Bild 4 zu sehen, werden die in einem Netz verbundenen Komponenten mit entsprechender Pin Bezeichnung dargestellt. Zur besseren Visualisierung kann per Klick in die Layout-Ansicht gewechselt werden. Der PCB-Viewer markiert die fehlerhaften Netzbereiche.

Leichte Implementation in den Produktionstest

Je nach Ausrichtung und Kapazität der jeweiligen Elektronikproduktion, kann die Integration von Boundary Scan verschiedenartig erfolgen. Nachfolgend wiederum Diatem als Beispielsystem:

Als Einzelprüfplatz „Stand-alone“:

Dieser Prüfplatz besteht dann aus einem PC (oder auch Notebook) mit der installierten Diatem-Production-Station bzw. Repair Station, einem Hardware-Controller (z.B. USB Controller, oder PCI-Karte) und dem(n) zu testenden Board(s) selbst.

Die Test- und Diagnosefunktionen von Diatem müssen nicht zwangsläufig über die von Temento mitgelieferte grafische Anwenderoberfläche aufgerufen werden. Diatem ist eine Serverapplikation, die z.B. auch unter populären Programmen wie LabView oder LabWindows lauffähig ist.

Als integrierte Lösung in ATE-Systemen (ICT, FP):

Dass Boundary Scan in Kombination mit ICT zweifellos zu einer wesentlich höheren Gesamttesttiefe führt, wird allein schon durch den Trend unterstrichen, der ATE Hersteller entweder eigene Lösungen anbieten oder auf Partnerschaften mit spezialisierten Boundary-Scan-Systemherstellern setzen lässt.

Zu erwartende Unterschiede in der Leistungsfähigkeit eines eigenentwickelten Systems im Vergleich zum Produkt eines spezialisierten Herstellers, sind nicht verwunderlich. Schließlich ist der Standard IEEE1149.1 nicht gleichzusetzen mit einem Testsystem. Es kommt auf das Firmen-Know-how und den Vergleich objektiver Leistungsparameter an. Wie hoch ist die Testabdeckung? Wie gut sind die Diagnosemöglichkeiten?

In Bezug auf das Beispiel des Diatem-Testers sind hier wiederum alle Optionen offen: Implementierung der Diatem-Production-Station in das ATE System. Oder auch Nutzung des in einem ATE System vorhandenen JTAG Features mit nachfolgender genauerer Diagnose im Fehlerfall über die Diatem Repair Station.

Fazit und Zusammenfassung

Leichte Integrierbarkeit von Boundary Scan in die Produktion heißt somit, vor allem offene Standards, flexible und modulare Lösungen vorzufinden, die der Vielfalt der Produktionsumgebungen entspricht: Vom separaten Einzeltestplatz bis hin zur Vollintegration in ATE Systeme. Im Beispiel des DIATEM® Testers liegen die Integration erleichternden Schwerpunkte klar auf Schnittstellen Standards (C/C++, DCOM), offenen Formaten (TCL, JAM, SVF…), und die gänzliche Absage an proprietäre Programmiersprachen (Bild 5).

Mit Blick auf die am Anfang des Beitrages formulierten Anforderungen lässt sich feststellen:

Mit dem Einsatz von Boundary Scan im Produktionstest, in Ergänzung zu herkömmlichen Testverfahren (wie z.B. ICT und FT), wird eine höhere Gesamttestabdeckung erreicht. Auf Grund des komplementären Wirkens des Verfahrens werden bisherige Beschränkungen herkömmlicher Testverfahren bzgl. Kontaktierbarkeit und Fehlerdiagnose kompensiert. Qualität wird auch bei komplexen Projekten sicher gestellt!

Boundary Scan kommt Bereichs- bzw. Abteilungs-übergreifend zum Einsatz, und beginnt bereits parallel zur Produktentwicklung. Beim Übergang zum Produktionstest liegt der Test bereits fertig vor und kann zeitnah im Sinne des schnellen Testens ausgeführt werden. Modifikationen sind ebenfalls rasch zu realisieren. Etwaige Wartezeiten für Adapter-Zubehör entfallen.

Als programmierbares, adapterloses Verfahren ist Boundary Scan flexibel, wirtschaftlich und amortisiert sich schnell. Einmalige (heute sehr günstige) Anschaffungskosten stehen extreme Zeiteinsparungen sowohl in der Programmerstellung als auch der Fehlerdiagnose gegenüber. Zudem reduzieren sich Kosten herkömmlicher Verfahren, z.B. durch teilweise, manchmal auch vollständige Substitution von sonst erforderlichem Testzubehör, wie zum Beispiel Testnadeln beim ICT.

Productronica, Stand A1.138

EPP 501

Literaturhinweis:

[1] Boundary Scan mit Diatem: FAQ – Fragen und Antworten; PDF-Broschüre, Temento Systems, Aug. 05

[2] Electronic Engineering mit Boundary Scan: Board-Test nicht nur für die Produktion; PDF-Broschüre, Temento Systems, Sept. 05

Über Temento Systems:

Temento Systems S.A. entwickelt und vertreibt Test & Debug-Lösungen als Soft- und Hardware, für Test Automatisierung elektronischer Produkte, im speziellen von SoC (System on Chip), FPGA, Leiterplatten/Boards, MCMs (Multi-Chip-Module) und Systemen. Anders als traditionelle EDA-Software-Anbietern positioniert sich Temento mit einer großen Bandbreite von Lösungen, unter Ausrichtung auf den System-Design-Test, beginnend im frühst möglichen Design-Stadium (Virtual Test) bis hin zum Hardware-Test (Physical Test). Lösungen von Temento werden von verschiedenen Teams in Entwicklung, Fertigung und Wartung/Reparatur genutzt, überwiegend in Unternehmen der Branchen Halbleiter, Consumer-Elektronik, Computer, Automotive bzw. Luft- und Raumfahrt

Unsere Webinar-Empfehlung

10.10.22 | 10:00 Uhr | Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine…

Teilen: