Eine der Herausforderungen für die Testingenieure wäre es, festzustellen, wann ein Test für eine bestimmte Leiterplatte „ausreichend“ ist. Die Ingenieure könnten zahllose Stunden und Wochen damit verbringen, einen weiteren Prozentpunkt an Testabdeckung herauszuholen, wenn nicht immer mehrere Boards auf sie warten würden. Es gilt also einen Punkt zu finden, an dem der Test für ausreichend erklärt wird. Danach kann sich der Ingenieur der Entwicklung von Teststrategien für die nächsten Projekte zuwenden. Aber wie soll der Testingenieur den Zeitpunkt bestimmen, an dem er sagen kann, es reicht?

Reg Waller, Asset InterTech, Stevenage (UK)

Bei Boundary Scan (IEEE 1149.1 oder allgemein auch JTAG genannt) kann eine umfassende Beschreibung der Fehlerabdeckung erheblich helfen. In diesen Berichten ist detailliert aufgeführt, welche Probleme festgestellt wurden, welcher Umfang an Testabdeckung erreicht wurde, wo keine gegeben ist und wie sie verbessert werden könnte.

Was ist ein Defekt?

Ein Defekt ist als ein Mangel im Fertigungsprozess definiert. Boundary Scan erkennt solche Defekte, die eine korrekte elektrische Verbindung zwischen Punkten auf einer Leiterplatte verhindern, die laut Designvorgabe verbunden sein sollten.

Beim Boundary-Scan-Testprozess erscheint ein Defekt als Fehler. Wird ein Fehler gemeldet, weist das darauf hin, dass der Test zu Ergebnissen geführt hat, die von den Erwartungen abweichen. Wenn beispielsweise der Pin eines Bausteins nicht korrekt auf das Board aufgelötet ist und kein elektrischer Kontakt zustande kommt, stellt ein Boundary-Scan-Test eine Unterbrechung des Stromkreislaufes fest, der als „stuck-at-1“- oder „stuck-at-0“-Fehler angegeben wird. Durch die Diagnose des Fehlers kann der zugrunde liegende Defekt (der falsch angelötete Pin) in der Regel gefunden und behoben werden. Ein weiteres Beispiel ist eine nicht vorgesehene elektrische Verbindung zwischen zwei oder mehr Pins bzw. zwischen Netzen auf einer Leiterplatte. Ein Boundary-Scan-Test stößt unter Umständen auf einen elektrischen Kurzschluss, auf den ein unerwartetes Muster von Nullen und Einsen hinweist, wobei durch weitere Diagnose dem Fehler ein physischer Defekt zugeordnet wird und damit das Board repariert werden kann. Durch Tests werden Fehler gefunden, durch deren Beseitigung Defekte der Leiterplatte behoben werden. Die Testabdeckung ist eine Maßzahl dafür, wie viele Fehler ein bestimmter Boundary-Scan-Test aus der Gesamtzahl möglicher Fehler finden kann.

Beschreibungen der Fehlerabdeckung, die von Boundary-Scan-Testsystemen erstellt werden, ermöglichen oft eine Beurteilung darüber, wie gut ein Test die Fehler erkennen wird, die Boundary Scan entdecken kann. Der Report könnte beschreiben, wieweit ein Test die Gesamtmenge potenzieller Fehler abdeckt. Das ist aber nur dann wirklich sinnvoll, wenn die Testsuite in der Lage ist, alle potenziellen Fehler zu erkennen, was Boundary Scan nicht leisten kann. Ein wesentlich sinnvollerer Boundary-Scan-Report befasst sich deshalb nur mit jenen Fehlern, die durch Boundary Scan auch erfasst werden können. Diese Art von Bericht könnte Input für eine umfassende Beschreibung der Testabdeckung liefern, die Reports aus anderen strukturellen Testtechnologien enthält wie beispielsweise aus Incircuit-Testsystemen, Flying-Probe-Testern oder Messgeräten zur Feststellung von Fertigungsdefekten.

Berichte über Fehlerabdeckungen bieten zudem eine wichtige Hilfestellung, wenn sie darauf hinweisen, dass das Design eines Boards unter Umständen nicht genügend Merkmale für Boundary-Scan-Tests aufweist. So ist ein Test unter Umständen zwar in der Lage, 100 Prozent aller Defekte zu erkennen, die Boundary Scan feststellen kann. Wenn aber die Boundary-Scan-Testfähigkeit nicht komplett im Boarddesign implementiert ist, könnte es sein, dass Boundary Scan nur zehn Prozent aller potenziellen Defekte auf der Leiterplatte erkennt. Solche Ergebnisse könnten als Warnung für Design- und Testingenieure dienen, dass sie zusätzliche Testabdeckungsfunktionen (in der Regel DFT – Design-for-Test – genannt) in das Design einbauen müssen, um Vorteile aus den Funktionalitäten von Boundary Scan zu ziehen.

Fehler können entweder direkt von Boundary-Scan-Tests festgestellt werden, die speziell zur Fehlererkennung generiert werden, oder auch von anderen Boundary-Scan-Operationen wie beispielsweise dem Laden von Daten oder Programmen in Speicherbausteine auf der Leiterplatte. Beispielsweise werden Boundary Scan Interconnect-Tests oder Verifizierungstests für den Speicherzugriff speziell dafür erzeugt, um die Verbindungen zwischen Bausteinen zu prüfen, wobei eine Flash-Programmieroperation zum Ein- und Auslesen von Flash-Memory-Daten dient. Als Nebenprodukt dieser Ein-/Auslese-Operation werden auch die Verbindungen zwischen einem Boundary-Scan-Baustein und einer Non-Boundary-Scan-Flash-Memory-Komponente geprüft.

Reports über Interconnects

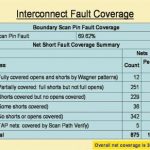

Boundary-Scan-Tests können Kurzschlüsse und fehlende Verbindungen auf Boardnetzen und Bausteinpins feststellen. In der Regel wird die Testabdeckung auf einem Netz als vollständige, teilweise oder fehlende Abdeckung klassifiziert. Reports zur Abdeckung können ganz verschieden strukturiert sein. Damit ein Ingenieur möglichst großen Nutzen aus einem Bericht ziehen kann, sollte er unbedingt wissen, wie er zustande gekommen ist.

Der Boundary-Scan-Testprozess besteht aus der Anwendung von Testmustern auf einer Leiterplatte und der anschließenden Überprüfung, ob der Test die Ergebnisse liefert, die anhand der Designdaten zu erwarten waren. Fehler auf einer Leiterplatte können dazu führen, dass die tatsächlichen Resultate eines Boundary-Scan-Tests von den erwarteten Resultaten abweichen. Die meisten Boundary-Scan-Testmuster werden so optimiert, dass sie ein umfassendes Maß an Abdeckung mit der geringsten Anzahl an Mustern bieten. Beispielsweise können Muster zur Erkennung von Kurzschlüssen zwischen zwei Netzen auch alle „Stuck-at“-Fehler erkennen. Die am häufigsten benutzten Algorithmen sind die so genannten Wagner-Muster oder modifizierten Wagner-Muster (Eine eingehende Erklärung zu diesen Algorithmen ist unter www.asset-intertech.com/pdfs/boundaryscan_tutorial.pdf zu finden).

Weitere Testmuster wie beispielsweise „Walking Ones and Zeros“ können die Diagnose von Fehlern erleichtern, aber das Thema sprengt den Rahmen dieses Artikels.

In einem Fehlerbericht eines Boundary-Scan-Tests wie beispielsweise des ScanWorks Systems von Asset InterTech wird die Interconnect-Fehlerabdeckung eines Tests dokumentiert, der anhand der Input-Parameter generiert wurde, die der Testmuster-Generierungs-Engine von ScanWorks zur Verfügung gestellt wurden. Die Genauigkeit des Testabdeckungsberichts lässt sich verbessern, indem der Test-Engine weitere Informationen zur Verarbeitung geliefert werden. Das geschieht oft durch Bereitstellung weiterer Modelle von Non-Boundary-Scan-Bausteinen oder durch Definition von Randbedingungen, die weitere Tests ermöglichen. Im Allgemeinen geht bei ScanWorks die Sicherheit der Leiterplatten vor. Das heißt, es wird kein Test für ein Netz generiert, für das nicht ausreichend Informationen darüber zur Verfügung stehen, wie sicher der Test des Netzes wäre. Damit ein Boundary-Scan-Test sicher ist, darf nie mehr als ein Treiber für ein Netz zu einem bestimmten Zeitpunkt vorhanden sein. Wenn ScanWorks nicht sicher sein kann, dass nur ein Treiber auf einem Netz aktiv ist, wird es das Netz keinem Test unterziehen, um dessen Sicherheit nicht zu gefährden. Mehrere Treiber auf einem Netz lösen zwar nicht unbedingt einen unmittelbaren Fehler aus, könnten aber einen latenten Defekt verursachen, der aber erst zutage treten würde, wenn die Leiterplatte schon an die Kunden ausgeliefert wurde.

Die Erweiterung der Boundary-Scan-Testabdeckung

Sollte der Bericht zur Fehlerabdeckung eines Boundary-Scan-Systems auf eine niedrige Abdeckung hinweisen, könnte der Abdeckungsgrad durch Erweiterung der Boundary-Scan-Tests auf Non-Boundary-Scan-Bausteine erhöht werden.

Einige Boundary-Scan-Systeme wie ScanWorks von Asset InterTech sind dazu in der Lage, wenn die Test-Generierungs-Engine des Systems über genügend Informationen zu den Non-Boundary-Scan-Bausteinen verfügt. Das Boundary-Scan-System muss auch über genügend Informationen verfügen, um zu erkennen, ob es sicher ist, Netze mit Verbindungen zu Non-Boundary-Scan-Pins zu testen.

Boundary Scan Interconnect-Tests können ebenfalls auf Non-Boundary-Scan-Bausteine angewendet werden, wenn diese mit einer Boundary-Scan-Komponente verbunden sind. Dazu können die I/O-Eigenschaften und die Transparenz des Non-Boundary-Scan-Bausteins für jeden Pin auf der Komponente manuell zur Verfügung gestellt werden. Alternativ können diese Informationen der Testgenerierungs-Engine in Form eines „Cluster“-Modells übergeben werden. Zudem kann ein Cluster-Modell auch die Input-Pin-zu-Output-Pin-Logik für einfache Bausteine beschreiben. Beispielsweise würde das Cluster-Modell für einen 245-Puffer-Baustein jeden I/O-Pin als bidirektional beschreiben. Das Modell würde zusätzlich die Input-zu-Output-Beziehungen für jeden Pin abbilden. Die Pins für die Richtung und Tri-State-Beschaffenheit des Bausteins sind ebenfalls im Cluster-Modell definiert, wodurch die Test-Generierungs-Engine in die Lage versetzt wird, die Steuerpins automatisch so einzustellen, dass Boundary-Scan-Testmuster in jede Richtung passieren können, solange die 245 Bausteinpins mit den Boundary-Scan-Pins in beide Richtungen verbunden sind. Anhand solcher Informationen kann eine Test-Generierungs-Engine mit vollständigem Funktionsumfang wie die von ScanWorks nicht nur die verfügbare Abdeckung von der teilweisen bis zur vollständigen Abdeckung für alle Boundary-Scan-Pins auf der Leiterplatte erhöhen, sondern auch zusätzliche Testabdeckung für Pins auf bestimmten Non-Boundary-Scan-Bausteinen bieten.

Zusammenfassung

Berichte über die Fehlerabdeckung spielen eine wichtige Rolle bei der Entwicklung und Implementierung von Boundary-Scan-Testsuites mit hohem Abdeckungsgrad. Darüber hinaus kann ein umfassender Boundary-Scan-Report dokumentieren, wo es sich lohnt, zusätzliche Designarbeit in die Integration von Design-for-Test-Funktionen und Testfähigkeitsfeatures zu investieren, um einen signifikanten Nutzen für die Fertigung, den Kundendienst und den gesamten Lebenszyklus des Produkts zu erzielen.

EPP 485

Unsere Webinar-Empfehlung

Auch dieses Jahr präsentiert Koh Young wieder aktuelle Trends und „State of the Art“ Technologie aus der optischen Inspektion und 3D-Messung auf der Productronica in München. Aber wir alle kennen das Problem voller Terminkalender, Reisebeschränkungen oder fehlender Zeit, um in…

Teilen:

.png)