Bereits heute kann man sagen, daß die demnächst auf dem Nürnberger Messegelände stattfindende SMT diverse eigene Rekorde schlagen wird. Der Mesago-Geschäftsführer Joseph Rath: „Deutlich über 650Aussteller werden auf Europas führender Messe für Systemintegration in der Mikroelektronik ihre Produkt-highlights dem Fachpublikum präsentieren“. Der Veranstalter meldet neben dem Zuwachs bei der Ausstellerzahl auch einen in der Fläche, zudem steigt die Internationalität weiter.

Neben der SMT-Fertigung, die den Löwenanteil stellt, sind in den Bereichen Test, Hybride, Packaging und Auftragsfertigung weitere Aussteller ver-treten. Die munter anwach-sende Veranstaltung belegt nun 27.000qm Fläche (Vorjahr 24.000qm). Insgesamt sind mehr als 650 Aussteller angemeldet, auch die Besucherzahl wird die letztjährigen 25.467 überschreiten. Die Vorteile des allgemein einfach SMT genannten Branchentreffs sind nicht zu verachten: Konzentration auf einen gut definierbaren Industriebereich, ein gut erreichbarerStandort mitten in Europa, nicht zu weit von High-Tech- bzw. Fertigungsregionen entfernt, jährlicher Rhythmus (spiegelt Innovationszyklen optimal wider), außerdem läßt die Terminlage Mai oder Juni noch genügend Zeit im laufenden Jahr fürs nötige Follow-up.

Der diesjährige Event umfaßt auch jeweils einen Gemeinschaftsstand für englische und US-Unternehmen. Das gibt Aussteller aus diesen Regionen die Möglichkeit, hier Schwerpunkte zu bilden. Und natürlich ist dies für die Firmen auch noch ein leichterer Einstieg in bislang nicht bekannte, ausländische Märkte. Circa ein Drittel der Besucher kommt aus dem Ausland, überwiegend natürlich aus europäischen Ländern.

Der Kongreß unter dem Vorsitz von Herbert Reichl vom Fraunhofer IZM in Berlin, bietet Experten aus Industrie und Wissenschaft über drei Tage hinweg eine hochkarätige Veranstaltung. Um der ständig wachsenden Nachfrage aus Europa, Asien und Amerika gerecht zu werden, wird der Kongreß erstmals in englischer Sprache durchgeführt. Ein besonderer Höhepunkt zu Beginn der Veranstaltung ist der Dienstagnachmittag (27. Juni). Referenten aus drei Kontinenten referieren unter anderem zu folgenden Themen: Electronics and Environment, Microvia Technology, CSP versus BGA Assemblies. Am 28. Juni stehen Vorträge zu aktuellen Themen der Mikroelektronik auf dem Programm: Produktneuheiten sowie Lösungen und Entwicklungen der Branche werden in den Bereichen Components, Interconnect Technologies, Assembly, Lead-Free Solders, Substrate, Quality Assurance, Quality Management und Future Trends vorgestellt. Abgerundet wird das Programm mit praxisnahen Tutorials. Auch hier sind interna-tionale Referenten engagiert, die Themenbereich vertiefen und anwenderorientiert aufbereiten: Polymers for Electronic Packaging, Lead-free, Introduction to Simultaneous Double Sided Reflow Soldering, Flex Circuits, Flip Chip in Produktion oder Kleben und Löten – um nur einige zu nennen.

Markt-informationen zur Fertigung

Wie Uwe Fuhrmann vom VDMA-Fachbereich Productronic erläutert, rechnet man sich in Europa Chancen aus, im weltweiten Elektronikgeschäft eine gute Position einzunehmen. Europa ist der zweitgrößteMikroelektronikanwender, zudem befinden sich unter den größten Halbleiterherstellern mit STMicroelectronics, Infi-neon und Philips auch drei Firmen europäischer Herkunft. Die tragenden Säulen des Wachstums sind speziell die Kfz-Elektronik, Datentechnik und Telekommunikation. Im Halbleitermarkt ist die Rezes-sion überwunden und es geht steil aufwärts. Das Jahr 1999 schloß man mit einem weltweiten Volumen von 149 Mrd. US$ ab (+ 18,9%). Für die Jahre 2000 und 2001 wird entsprechend der Nachfrageentwicklung ein Wachstum von über 20% prognostiziert. Für Deutschland erwartet man noch höheres Wachstum (circa 23%). Der Fachverband Bauelemente im ZVEI sieht für die Datentechnik ein Plus von 25%, für die Telekommunikation 34% und die Kfz-Elektronik rund 15%. Auf das Equipment für Halbleiterfertigung kommt wieder stürmische Nachfrage zu. In 1999 kam nach Angaben von SEMI mit einem Umsatzzuwachs von 16,8 % ein Volumen von 24,5 Mrd. US$ zustande. Die regionale Verteilung zeigte, daß Taiwan davon 18 % abnimmt, die USA 29 %, Japan 22 % und Europa 13%. Für die nächsten sechs Monate erwartet man 12 bis 18 Projekte für Halbleiterfabriken und insgesamt 40 neue Projekte über1 ½ Jahre. Nach dem Start der weltweit ersten 300-mm-Linie bei Infineon in Dresden nehmen auch wieder solche Projekte zu.

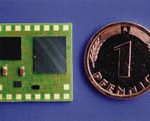

Mehr oder weniger unbehelligt von den Zyklen der Bauelementeindustrie wächst der weltweite Leiterplattenmarkt kontinuierlich jährlich 6 bis8 %. Das Gesamtvolumen weltweit wird sich auf rund 37 Milliarden US$ belaufen, sagtUwe Fuhrmann. Die Zuwachsrate bei Rigid-Boards lagen bei 6 % lag und bei flexiblen Leiterplatten bei 16 %. Füretwa die nächsten 20 Jahre kündigt sich ein umfassender Paradigmenwechsel in der Elektronikfertigung an. Dabei wird die Aufbau- und Verbindungstechnik (Packaging) sowohl auf Wafer- als auchBoardlevel zur Schlüsseltechnologie und bestimmt maßgeblich die Funktionalität, Qualität und Wirtschaftlichkeit der Schaltungen. Die Forderungen nach weiterer Verringerung von Größe, Gewicht und Energieverbrauch lassen sich nur über neue Packagingtechniken erzielen. Dabei rückt der Reinraum aus der Halbleiterfertigung der Baugruppe immer näher. Derzeit werden drei Hauptrichtungen der Integra-tion verfolgt: Bei Systems-on-a-Chip (SoC) bringen Entwickler ihre Expertise in gemeinsamen Strategien als Intellectual Property (IP) in den Chips ein. Auf dem Halbleiter werden unterschiedliche Building-Blocks zu einem Sy-stem zusammengefügt. Wafer-Level-Packaging (WLP) ermöglicht durch Verwendung nackter Chips (Dies) und daraus resultierenden geringeren Platzbedarf einen höheren Integrationsgrad. Flip-Chip und Chip-Scale-Packaging (CSP) sind Beispiele dafür. System-in-a-Package (SiP) ist die funktionale Integration von Subsystemen. Angesprochen sind hier unterschiedliche Techniken, wie die Implementation von diskreten, passiven und aktiven Bauelementen zu Mikromodulen in einem „klassischen“ IC-Gehäuse (DIL),das 3-D-Packaging (Stapeln/ Stacking von Packages oder von Chips in einem Package, sowie der Flip-Chip-in-a-Package (FCIP).

Paradigmenwechseldurch Packaging

Um den Anforderungen, die sich aus der Produkt- undChipentwicklung ergeben (leistungsfähig, klein, leicht, mobil, autonom, kostengünstig) zu genügen, sind optimale Auswahl von Materialien sowie die Entwicklung effizienter Fertigungs- und Prüftechniken im Packaging notwendig. Die Zielsetzung für die nächsten10 Jahre ist eine Steigerung der Leistungsfähigkeit um den Faktor 2 bei einer Reduzierung der Kosten um den Faktor 4. Entsprechend dem Trend weiter steigender Anschlußzahlen (1000) bei verkleinerten Kontaktabständen (Pitch 65µm) bei Betriebsfrequenzen von1 bis 5GHz sind die Anwendungsmöglichkeiten konventioneller Kontaktiertechniken (Drahtbonden) begrenzt, im Bereich noch höherer Frequenzen auszuschließen. Deshalb konzentrieren sich die Entwicklungsarbeiten im Packaging auf direkte Chipmontage (Direct-Chip-Attach, DCA) mit Chip-on-Board (COB) und Flip-Chip (FC), Chip-Scale-Package (CSP) und Ball-Grid-Array (BGA). Wichtige Gesichtspunkte dabei sind:

• Materialcharakterisierung (Modell, Simulation und Messung)

• Ultradünne Si-Chips (50 µm)

• Cu-Metallisierungen im Halb-leiter

• Kostengünstiges Bumping und Umverdrahten

• Feinlagen- und Mehrlagentechnik für Waferlevel-Packaging

• Prozeßkompatibilität mit SMT- Technik

• Hochautomatisierte Fertigung

• Umweltverträgliche Materialien und Prozesse

Mit Multichipmodulen und deren Weiterentwicklung für High-Density-Interconnect wurde eine weitere Ebene in der Hierarchie der Aufbau- und Verbindungstechnik eingeführt, die die Rea-lisierung optimierter Subsysteme vereinfacht. HDI stellt im Packaging eine sehr komplexe Technik mit hohen Ansprüchen dar. Neben der Steigerung der Systemperformance sind auch Volumen- und Kostenreduzierungen zu erwarten, zudem eröffnen sich Wege zur Integration von Chips grundverschiedener Technologien (GaAs/Si) in einem System. Die Vorzüge von HDI basieren auf der Verwendung unge-häuster Chips. Die Reduzierung der Kontaktierungen resultiert in höherer Zuverlässigkeit. Gegenwärtig werden alle Substrat-Techniken (MCM-L, MCM-C, MCM-D) in einem breiten Spektrum von FC-Modulen in Dünnfilmtechnik auf keramischen Trägern über Mehrschichtkeramiken bis hin zu Chip-on-Board mit Leiterplatten eingesetzt. Entscheidend vorangetrieben werden derartige Systeme auf flex-iblem Trägermaterial durch Anwendungen im Mobilfunkbereich, der Informations- und Kommunikationstechnik sowie bei der Automobilelektronik.

gbw

EPP 209

Unsere Webinar-Empfehlung

Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine zeitnahe schnelle Messung…

Teilen:

.png)