Beim 3D-IC-Packaging werden drei oder mehr übereinander angeordnete Chips zusammen mit den erforderlichen passiven Komponenten integriert. Die Vorteile sind kos-tengünstigere Fertigung, einfacheres Handling beim Fertigungs- und Montageprozess sowie geringerer Platzbedarf. Außerdem weisen die Packages eine höhere Zuverlässigkeit und bessere elektrische Performance auf.

Amkor hat die Entwicklung und Qualifikation von 3D-IC-Packages in diesem Jahr erweitert. Anfangs nur für Mobilte-lefone und andere mobile Anwendungen verwendet, reichen die Einsatzgebiete mittlerweile bis hin zu Internet-Routern, Switches, Basisstationen, PDAs und PCs. Nach einer Studie von Techsearch International werden dieses Jahr etwa 230 Mio. 3D-ICs hergestellt werden, bis Ende 2002 wird ein Wachstum auf 348 Mio. Stück erwartet.

Die Vorteile der 3D-Technik kommen vor allem bei den Kos-ten zum tragen. So reduzieren sich für den Chiphersteller die Bauteilkosten: Während jedes einzelne IC-Package sein eigens hochpoliges Verbindungs-substrat (das teuerste Material im Package) benötigt, ist für ein 3D-Package nur ein Substrat oder eine Zwischenplatine erforderlich. Dadurch können die Kosten um bis zu 35 % niedriger sein.

Zudem verringert sich der Test-aufwand im Vergleich zu drei oder mehreren einzelnen Chip-Packages. Ebenso wird das Tes-ten während der Board-Montage einfacher, da das Handling der Bausteine im allgemeinen mehr Zeit in Anspruch nimmt als der Test selbst.

Der Flächenbedarf auf den Sys-tem-Boards wird durch die 3D-Packages um 30 bis 60 % reduziert. Die Verdrahtung innerhalb verringert die äußere Anschlussdichte, wodurch größe-re Abstände für die Mon-tage-Pads möglich sind. Daher entstehen geringere Montagekosten und die Zuverlässigkeit der nachgeordneten Lötverbindungen ist erhöht. Weitere Ein-sparungen entstehen durch die geringere Zahl an Bauelementen, die beschafft, qualifiziert, inventarisiert und verarbeitet werden müssen. Die 3D-Montagetechniken erlauben unterschiedliche Verbindungstechniken innerhalb eines Packages. Dazu gehören Chip-zu-Chip, Chip-zu-Substrat sowie Kombinationen aus Draht-Bonding oder Flip-Chip-Techniken. Mit Hilfe von Wafer-Thinning und dünnen Substraten wird bei drei Chips eine Höhe von 1,4 mm und bei zwei Chips1,2 mm erreicht. Das Gewicht kann im Vergleich zu einzelnen ICs um bis zu 70 % reduziert werden.

EPP 157

Unsere Webinar-Empfehlung

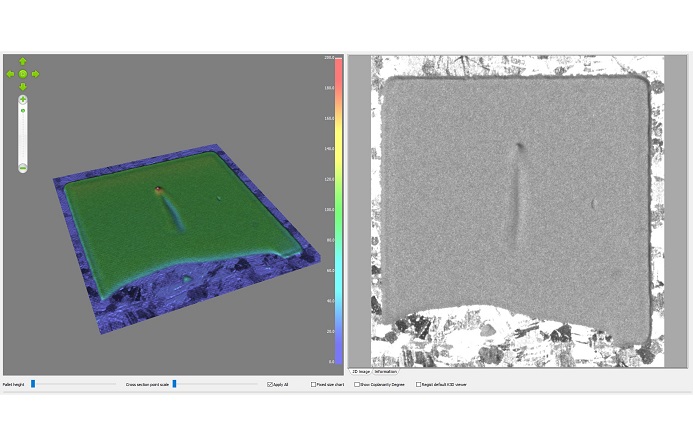

Applikationen aus dem Bereich der Leistungselektronik gewinnen immer mehr an Bedeutung. Die Inspektion dieser Applikation lässt sich mit der bewährten Standardtechnologie der 3D-Messtechnik bewerkstelligen.

Teilen: