Eine der wichtigsten Neuentwicklungen im Bereich von Halbleiter-Packaging und Laminat-Technik sind S-CSPs (Stacked-Chip-Scale-Packages). Die von Amkor perfektionierte 3D-Fertigungsmethode beruht darauf, dass man mehrere dünne, ungehäuste Chips direkt aufeinander montiert. Die jetzt zur Verfügung stehende Baustein-Packaging-Methode ist das erste Low-Cost-Verfahren, die Anwendung wird überwiegend von den Miniaturisierungsanforderungen portabler Geräte forciert. Erst diese Technik ermöglicht weitere Geräte-Miniaturisierungen mit noch höheren Funktionsdichten.

Amkor, Chandler, USA

Der größte Vorteil von S-CSPs ist, dass solch ein Bauteil, das beispielsweise aus zwei Chips und einer passiven Komponente bestehen kann, die gleichen Einbaumaße wie ein üblicher IC aufweist. Das Laminat dient dabei als Substrat, das die Basis für ein äußerst schmales Advanced-Package darstellt. Dieses Substrat ist ein dünner dielektrischer Film mit einer Kerndicke von 100 oder 150 mm, der bis zu vier Lagen für elektrische Verbindungen bereitstellt. Mit der von Amkor entwickelten Technik lassen sich momentan maximal drei ungehäuste Chips (Dies) zu einem gehäusten Bauteil zusammenfügen, das nur 1,4 mm dick ist. Dies einschließlich der Lotkügelchen (Solder-Balls) mit Durchmessern von 0,3, 0,4 oder 0,46 mm für die Verbindung vom Package zum Board. Das Ergebnis ist ein Bauteil mit niedrigem Profil, ein SIP (System-in-a-Package) mit einem Standard-Anschlussraster nach JEDEC MO-219. Solche ICs lassen sich wesentlich einfacher und kostengünstiger herstellen als ein klassisches SoC (System-on-a-Chip) mit allen Funktionen auf einem Chip. Hingegen kann jeder einzelne Chip in einem SiP gezielt mit dem optimalen Frontend-Prozess hergestellt werden, beispielsweise für optimale HF-Eigenschaften oder schnellste digitale Signalverarbeitung. Das verbessert die Performance, Produktionsausbeute und verkürzt auch noch die Zeit bis zur Markteinführung. Man kann somit feststellen, dass solch ein SiP für kundenspezifische Bausteine, optimal an die Applikation angepasst (Scaleability), eine besonders geeignete Lösung darstellt.

Amkor, der 1968 gegründete Hersteller solcher Bausteine, verfügt über eine umfassende Expertise im Halbleiter-Packaging und ist deshalb in der Lage, alle einzelnen Fertigungsschritte mit großer Umsicht zu realisieren. Das weite Produkt-Portfolio umfasst als Kernkompetenzen Packaging-Entwicklung und Charakterisierung, Wafer-Foundry-Service sowie Test und IC-Packaging. Für Auftraggeber, die auf dieses Portfolio zugreifen, sind die Investitionen und das Risiko bei der Einführung neuer Packaging-Methoden relativ gering und leicht kalkulierbar. Gleichzeitig ist jedoch voller Zugriff auf den aktuellen Stand der Technik gegeben. Amkor hält als Marktführer einen weltweiten Marktanteil von etwa 50 % in der Substrat-Technologie und in der Fertigung von BGAs auf Laminaten. Die vom Unternehmen entwickelte 3D-Packaging-Methode basiert im Grunde auf vielen einzel-nen Fertigungstechniken. Dazu gehören Stacked-CSP (IC bzw. ASIC plus Spei-cher), Stacked-Die-Leadframe (Baustein mit außenliegenden Pin-Anschlüssen wie TSOP, QFP, MLF), Flip-Stack (gedrehte – geflippte – Chips, verbunden durch WireBonding), Die-Stack auf PBGA, Flex-PBGA sowie Die/Package-Stack. Die Zwischenverbindungen in den SiP-Bausteinen werden mit Drahtbonds hergestellt, auch passive Komponenten lassen sich hier relativ leicht integrieren.

Bei der nun vorgestellten und perfektionierten Fertigungstechnik für S-CSPs nutzt das Unternehmen uneingeschränkt seine Expertise im Bereich der BGAs sowie Advanced-Packaging, wobei noch die Möglichkeit hinzukommt, mehrere Dies aufeinander zu montieren (Stacking). Diese Bausteine sind verfügbar in vielen unterschiedlichen Konfigurationen und basieren auch auf einer dünnen Substrattechnik mit der Abdünnung von Wafern (bis zu einer geringen Dicke von nur noch 175 mm). Zusammen mit der BGA-Packaging-Technik, die eine Verdopplung der Speicherkapazität erlaubt, sind damit höher Baustein-Funktionsdichten möglich, wobei der Platzbedarf weiter reduziert ist. S-CSP offeriert zudem die Flexibilität, kundenspezifische Speicherentwicklungen mit Standard-Bauteilen zu kombinieren und dabei weitere Kostenreduzierungen zu erzielen.

Stacking – der Weg zu höherer Funktionsdichte

Zunächst ein kurzer Blick auf die wesentlichen Motive für diese Entwicklung. Allgemein geht man bei den Fortschritten in der Halbleiter-Technik von Moores Formel aus, die besagt, dass alle 18 Monate die Zahl der Transistoren oder Funktionen verdoppelt wird. Folgerichtig hat die Chip-Integration mittlerweile die Aufnahmefähigkeit der Leiterplatten für Verbindungen/Lötstellen sowie Bauelemente längstens überschritten. Hier werden die Geometrien ja immer noch im Submillimeter-Bereich definiert, bei Halbleitern hingegen ist man schon seit vielen Jahren im Submikronbereich angelangt. Auch diese Relationen der geometrischen Dimensionen verdeutlichen, dass die limitierte Aufnahmekapazität der sogenannten zweiten Verbindungsebene (Package/Board) die Möglichkeiten der Entwickler erheblich einschränkt, den vollen Funktionsumfang eines SoC (System-on-a-Chip) optimal auf die Baugruppe zu bringen.

Diese Tatsache stellt eine ernste Design-Herausforderung dar. Während die Anforderungen einerseits Reduzierungen bei Größe, Gewicht und Kosen vorsehen, müssen andererseits wesentlich höhere Funktionsumfänge der Schaltungen realisiert und dem Nutzer komplikationslos verfügbar gemacht werden. Ein Weg, hier die nötige Leistungsfähigkeit bereitzustellen, erfolgt über die dreidimensionalen Packages. Sie stellen die gewünschte hohe Baustein-Volumendichte durch die vertikale Montage mehrerer Chips (Stacking) bereit, wobei jedoch die Fähigkeit der Leiterplatte, für höhere IC-Integrationsdichten die nötigen Verbindungen bereitzustellen, nicht überfordert wird. Die mit dieser 3D-Methode in einem Package montierten ungehäusten Chips stellen einen wesentlich höheren Funktionsumfang bereit als andere Techniken auf der Basis mehrerer Packages.

Anwendungsvorteile durch S-CSP

S-CSPs mit der hohen Funktionsdichte ihrer integrierten Komponenten, die eine hohe Anschlusszahl aufweisen, be-ruhen auf dem Draht-Bonding der einzelnen Dies sowie dem Einsatz von HDI-Laminaten (High Density Interconnect). Damit lassen sich die höheren Verdrahtungsanforderungen auf der Gehäuseebene in den Griff bekommen. Das Ergebnis sind 3D-Bausteine, die sowohl mit reduzierten Leiterplatten-Verbindungen als auch einer deutlichen Minimierung an Flächenbedarf auskommen. Ingesamt sind damit auch erhebliche Einsparungen bei den Baugruppenkosten erzielbar.

Die direkten Einsparungen ergeben sich bei der Package-Montage durch die Integration von mehreren Chips in einem Gehäuse. Diese werden durch die indirekten Kostensenkungen ergänzt, die sich durch den Einkauf, das Handling und den Test von weniger Bauteilen ergeben. Als Folge führt das zu erheblichen Kos-tenvorteilen bei der Nutzung von 3D-Packages, die auf Chipsätzen, einer hohen Halbleiter-Integration oder großen Speicherblöcke beruhen. Als erste Anwender von CSPs (Chip-Scale-Packages) haben die Handy-Hersteller die Vorteile dieser kosteneffizienten Bausteinform in allen Applikationsformen erkannt. Industriebeobachter sehen beim CSP derzeit die größten Zuwachsraten unter allen Advanced-Packages, weil damit viele Anwendungen und Ausführungen möglich sind. Die Analysten von Prismark prognostizieren, dass bereits 2002 circa 10 % aller IC-Packages als 3D-Versionen hergestellt werden. Diese Vorhersa-ge rechnet mit etwa 40 Milliarden Bausteinen auf der Basis von Chip-Stacking. Die Marktforscher sprechen hier bereits von der vierten Welle in der Package-Innovation.

Höhere Funktionsumfänge

3D-Packaging ermöglicht, wie gesagt, höhere Funktionsdichten, einschließlich größerer Speicherkapazitäten, und erlaubt somit den Bau kleinerer Schaltungen, eine wesentliche Voraussetzung für alle mobilen Geräte. In dem Umfang wie immer mehr Funktionen in Geräten verfügbar sind, wobei die Frequenz-Bandbreite sowie die Speicherkapazität zunehmen, wird sich auch die Anwendung von S-CSPs ausweiten. Dabei wird sich die Technik aber nicht nur auf das Stacking von Flash- oder SRAM-Chips beschränken. 3D-Stacking wird in wesentlich größerem Umfang auch ASICs, Mixed-Signal- sowie Prozessor-Bausteine, DRAMs und andere hochintegrierte Speicher einschließen. Die unterschiedlichen Größen von Chips (Dies) und die nötigen Drahtbond-Verbindungen können dazu führen, dass mit speziellen Anordnungen der einzelnen Halbleiter und ihrer Montage aufeinander die Plazierung der Dies in einem SiP optimiert wird.

In einigen derzeit entwickelten Anwendungen geht es um die Anordnung von HF-Komponenten auf Logik-Chips. Dabei steht die Kontaktierung mit Flip-Chip bzw. BGA-Kontakthöckern (Bumps) im Mittelpunkt. Solche Lösungen sind denkbar für GPS, (Global Positioning System), Funkmodule oder Bluetooth. Für neue Handy-Generationen hat man drei Chips in S-CSPs integriert, um Basisband- und Speicherfunktionen in kleineren und kostengünstigeren Bausteingehäusen zu kombinieren. Erhebliche technische Fortschritte im Wafer-Abdünnen, Chip-Stacking und Wirebonden sowie bei HDI-Substraten ermöglichen die Optimierung von S-CSPs für spezifische Applikationen. Marktführer Amkor verfügt über die sehr reichhaltige Erfahrung und Expertise, die nötig sind, um kundenspezifische 3D-Konfigurationen, die höchste Leistungsanforderungen erfüllen, unter wesentlichen technologischen und Kostengesichtspunkten optimal herzustellen.

Kosten- und Leistungsvorteile durch Design-Aufteilung

Momentan weisen den höchsten Grad an Funktionalität nur SoC-Bausteine auf. Doch reicht die Fertigungstechnik für S-CSPs hier noch einen Schritt weiter und offeriert die Möglichkeit, das Schaltungs-Design in überlegt getrennte Blöcke für optimale Kosten- und Leistungsbedingungen aufzuteilen. Ein Chipdesign kann man entsprechend der Funktionen (analog, digital, HF, Speicher) in unterschiedliche Halbleiter aufteilen, die dann mit dem am besten dafür passenden Prozess gefertigt werden können. Im Gegensatz dazu lässt sich bei komplexen Mixed-Signal-Bausteinen oder Mixed-Technology-SoCs die Palette der Fertigungstechniken nicht in diesem weiten Umfang einsetzen, sondern sie kann in ihrem Einsatz nur auf die Hauptfunktion fokussiert werden. Durch die Aufteilung in unterschiedliche ICs (winzige CSPs), die in einem Gehäuse integriert sind (System-in-a-Package), lassen sich solche Schaltungen schneller, kostengünstiger und mit höherer Ausbeute herstellen. Die Vorteile sind somit offensichtlich.

Viele IC-Hersteller ohne eigenes Wafer-Prozess-Frontend (Fabless) verwenden das Konzept der Design-Aufteilung und die 3D-Packaging-Technik als wesentliche Bestandteile für den Ausbau ihrer Pläne im Bereich Produkt-Roadmaps und Systemintegration. Dabei geht ein starker Trend zum Stacking von drei Chips, um gezielt Anforderungen an höheren Speicherbedarf und einer möglichst kurzen Zeit zur Markteinführung zu entsprechen. Amkor hat seine Anstrengungen auf die Entwicklung und Qualifizierung einer ganzen Palette von Advanced-3D-Packages gelegt. Damit lassen sich unterschiedliche Baustein-Kombinationen realisieren sowie auch gezielt auf die erhöhten Anforderungen eingehen, die an Endprodukte gestellt werden. Speicher-Stacking ist jedoch momentan immer noch die dominante Applikation.

Anforderungen durch hochvolumige Anwendungen

Die vielen Vorteile des S-CSP haben sich bei der raschen Anwendung in portablen Geräten bewährt. Allerdings müssen einige wesentliche Fragen geklärt werden, bevor man 3D-Packages in sehr hohen Volumen einsetzen kann.

Bei S-CSPs handelt es sich im Grunde um sehr kompakt konzipierte Multi-Chip-Module, für die getestete Known-Good-Dies (KGD)sowie Burn-In-Prozeduren auf Wafer-Ebene nötig sind, um die nötige hohe Ausbeute nach dem Packaging zu erhalten. Der volle Funktionstest eines Bausteins, der aus mehreren unterschiedlichen Chips in einem Package besteht, ist stets eine sehr große Herausforderung. Deswegen müssen sowohl die Chipqualität absolut sicher-gestellt sein, als auch die Ausbeuten bei Substrat und Package-Montage praktisch 100 % erreichen. Außerdem muss bei eventuellem späteren Die-Shrinking darauf geachtet werden, dass keine Package-Änderungen nötig werden, denn diese haben ihrerseits eine erneute Qualifikation und diverse Kostensteigerungen zur Folge.

Auch der Bezug von ungehäusten Chips aus unterschiedlichen Lieferquellen kann durchaus kritisch sein, weil unter anderem auch die Die-Größen erheblich variieren können. Für die Opti-mierung von Kosten und Performance der SiPs sowie von Multi-Chip-Packages aller Art (inklusive 3D-Stacking) ist demnach eine sehr enge Zusammenarbeit zwischen dem OEM (Anwender), Package-Integrator sowie dem Halbleiter-Hersteller empfehlenswert. Erhebliche Vorteile können durch dieses Zusammenspiel genutzt werden.

Für ideale Bedingungen sollten die einzelnen Chip-Designs für das Stacking im Package optimiert werden, so in der Größe, der Stacking-Anordnung sowie dem Drahtbonding der Dies untereinander. Die Bemühungen, mit drei übereinander montierten Dies eine Gehäusehöhe von nur 1,7 mm einzuhalten (mit zwei Dies nur 1,2 mm), übt einen enormen Druck auf das Backend sowie das Wafer- und Die-Handling während der Assemblierung aus. Doch nur so lässt sich eine hohe Fertigungs-Ausbeute absichern.

Die Anordnung der Drahtbonds in den drei Dimensionen sowie die Länge und die Ausbildung der Draht-Loops muss sehr sorgfältig gewählt werden, um Kurzschlüsse oder Übersprechen zwischen den Chip-Anschlüssen zu vermeiden. Es gilt, Durchmesser und maximale Länge der Drahtbonds in Relation zu den Draht-toleranzen festzulegen, um die Ausbeute abzusichern.

Drahtbond-Anordnung sorgfältig auswählen

Amkor und Zuken haben gemeinsam ein spezielles Design-Tool für die Optimierung selbst äußerst kritischer Package-Konzepte entwickelt, um diese sicher fertigen zu können. Mit diesem 3D-Tool lässt sich der volle Bereich von unterschiedlichen Die-Abmessungen, geometrischen Positionierungen inklusive Rotation sowie Stacking- und die Bondpad-Platzierung für S-CSP überlegen für die Package-Montage umsetzen. Außerdem wurden wichtige Design-Regeln für 3D-Draht-profile und Bausteinhöhen entwickelt, die sicherstellen, dass solche Baustein-Packages in hohen Stückzahlen mit sehr hohem Durchsatz in hoher Ausbeute gefertigt werden können.

EPP 173

Unsere Webinar-Empfehlung

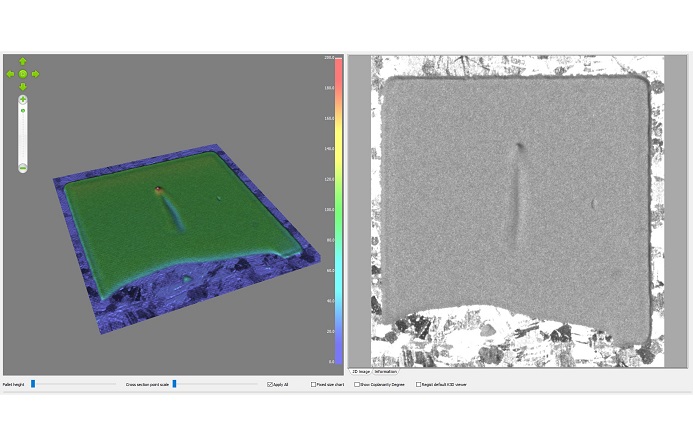

Applikationen aus dem Bereich der Leistungselektronik gewinnen immer mehr an Bedeutung. Die Inspektion dieser Applikation lässt sich mit der bewährten Standardtechnologie der 3D-Messtechnik bewerkstelligen.

Teilen: