Zum Aufbau und zur Qualifikation von Advanced-Packages, die jetzt zunehmend Verwendung finden, hat Binder Elektronik Interposer (Zwischenträger) für BGA-Bauelemente (Ball-Grid-Arrays) und Chip-Size-Packages (CSP) entwickelt. Mit solchen Interposern läßt sich der Aufbau von BGA- und CSP-Bauelementen einfach und wirtschaftlich untersuchen und qualifizieren.

Wolfgang Binder, Matthias Geiger, Binder Elektronik, Höpfingen-Waldstetten

Auf der Oberseite solch eines Interposers (Zwischenträger) werden die Flip-Chip-Komponenten mit ihren Daisy-Chain-Strukturen bestückt, auf der Unterseite sind die Lotkugeln aufgebracht. Solch ein Flip-Chip kann dann mit Vergußmasse eingehüllt werden. Diese Dummy-BGAs und -CSPs lassen sich auf ein Testboard bestücken und so mit einem Trainingskit, das im Rahmen eines vom BMBF geförderten Projekts entwickelt wurde, von Einsteigern in die Advanced-Packaging-Technik prüfen. Das Testkit enthält verschiedene Chips und Module sowie ein Auswertegerät (Future-Chip-Testboard), mit dem die Anwender die elektrische Funktion von maximal 24 Daisy-Chain-Strukturen auf den Testmodulen überprüfen können. Am Beispiel der BGA- und CSP-Interposer zeigen wir die verschiedenen Aufbau- und Verbindungstechniken, die auch als Dienstleistung verfügbar sind.

Die Interposer

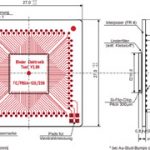

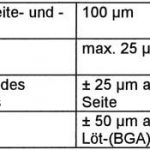

Das Design der Interposer (Zwischenträger) wurde bei Binder Elektronik anhand der Vorgaben nach den IPC-Standards und in Anlehnung an Bauelemente-Datenblätter durchgeführt. Der Interposer FC/PBGA-120/256 (Bild 1) eignet sich zum Aufbau eines Plastik-Ball-Grid-Array-Packages (PBGA). Die Abmessungen des BGAs betragen 27 x 27 mm. Der Ball-Pitch (Abstand von Lotkugel zu Lotkugel) beträgt 1,27 mm (50 mil). Der BGA weist vollflächig eine 16 x 16 Matrix auf, daraus resultieren 256 Ein- und Ausgänge. Auf der Oberseite läßt sich ein Flip-Chip (Silizium) mit 300-µm-Pitch und 120 Anschlüssen bestücken. Ferner ist eine Marke zum Kennzeichnen von Pin 1 sowie Passermarken als Positionierhilfen zum Bestücken vorhanden. Insgesamt weist der Chip 20 Daisy-Chain-Strukturen auf, die zu den BGA-Höckern auf der Unterseite verdrahtet sind. Damit auch die Kontaktierung der restlichen Balls überprüft werden kann, wurden noch vier weitere Daisy-Chain-Strukturen auf dem Interposer integriert. Anhand der Chips läßt sich auch eine Vierdrahtmessung der Übergangswiderstände von Interposer zum Flip-Chip durchführen. Dazu sind Pads auf der Interposer-Oberseite direkt neben dem Chip angeordnet. Der Zwischenträger besteht aus FR 4 mit 0,8 mm Dicke. Die Nickel/Gold-Oberfläche ist mit einer Lötstoppmaske zur Montage von Flip-Chips mit eutektischen Lotbumps versehen. Um auch die Montage von Chips mit Gold-Stud-Bumps und Gold-Pads zu qualifizieren, steht zudem eine Interposer-Version ohne Lötstopplack zur Verfügung. In Tabelle 1 sind die wichtigsten Design-Rules dieses Moduls zusammengefaßt.

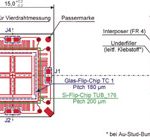

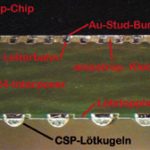

Der zweite Interposer FC/CSP-172 (Bild 2) ermöglicht den Aufbau eines Chip-Size-Packages mit der Kantenlänge 15 x 15 mm. Der CSP umfaßt 172 Lotkugeln im Pitch von 0,5 mm, ihr Durchmesser beträgt 0,3 mm.

Auf der Oberseite läßt sich wahlweise ein Flip-Chip mit 200-µm-Pitch und 184 IOs bestücken oder ein Glas-Flip-Chip. Da der Glas-Flip-Chip keine elektrischen Verbindungen hat, können die vier Daisy-Chain-Ketten mit Hilfe der Jumper (J1 bis J4) überbrückt und somit die Lotverbindungen des CSPs geprüft werden. Mit dem Glas-Flip-Chip kann man Fließverhalten des Underfillers und die Positioniergenauigkeit der Chips auf dem Interposer visuell kontrollieren. Bei diesem Interposer sind ebenfalls Pads für eine Vierdrahtmessung des Übergangswiderstandes von Zwischenträger zu Flip-Chip herausgeführt. Auch für diesen Interposer steht eine Version ohne Lötstopplack zur Verfügung, um Chips mit Gold-Stud-Bumps oder Gold-Pads in Klebetechnik zu bestücken. Material und Design-Rules entsprechen denen des FC/PBGA-120/256.

Aufbau der Packages

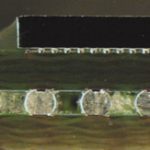

Mit den beiden Zwischenträgern lassen sich eine größerer Zahl von unterschiedlichen Aufbau- und Verbindungstechniken erproben und qualifizieren (Bild 3). Flip-Chips lassen sich auf den Interposern entweder löten oder kleben. Bei der Löttechnik wird der Chip vor dem Bestücken mit seinen Lotbumps in ein Flußmittel gedippt. Dabei ist darauf zu achten, daß nur die Bumps benetzt werden. Ist der Chip plaziert, wird per Reflow der Chip auf dem Interposer verlötet. Danach kontrolliert man das Bauelement elektrisch und optisch und führt – falls erforderlich – Nacharbeit durch. Anschließend folgt das Underfilling.

Werden Flux-Underfiller verwendet (Underfiller plus Flußmittel), wird zuerst der Underfiller appliziert, dann der Flip-Chip in den Flux-Underfiller gedrückt und im Reflow-Ofen gelötet. Der Flux-Underfiller härtet abhängig vom Typ teilweise oder vollständig aus, weshalb Nacharbeit nicht mehr ohne weiteres möglich ist.

Beim Kleben von Flip-Chips verwendet man Dies (ungehäuste Chips) mit Stud-Bumps oder Chemisch-Ni/Au-Bumps, ein Lötstoppmaske ist nicht nötig. Flip-Chips mit Gold-Stud-Bumps (Bild 5) weisen Golddrahthöcker als Kontaktierung auf, die mit einem modifizierten Wire-Bonder auf die Chippads gebracht wurden.

Klebetechnik

Es handelt sich um das einzige Verfahren, bei dem schon gesägte Wafer oder vereinzelte Chips (Dies) mechanisch mit Bumps versehen werden. Diese Methode ist besonders für Musteraufbauten und Kleinserien geeignet, bei denen eine Waferpräparation zu aufwendig und zu teuer wäre. Im Prinzip können wir Chips mit Gold-Stud-Bumps in drei Klebeverfahren herstellen.

Bei Verwendung von nichtleitfähigem Kleber wird dieser auf den Interposer dosiert, der Chip in den Kleber gedrückt und unter Druck und Temperatur ausgehärtet. Der gehärtete Klebstoff erzeugt durch sein Schrumpfverhalten die Zugkraft. Er drückt die Gold-Stud-Bumps auf die Pads des Interposers und stellt somit die elektrische Verbindung her. Als zweite Möglichkeit können Chips in anisotrop leitfähigem Klebstoff (nur in einer Richtung elektrisch leitfähig) montiert werden. Dazu wird ein Film oder Klebstoff mit anisotropen Eigenschaften auf den Interposer appliziert. Im nächsten Schritt wird der Chip mit den Bumps in den Klebstoff gedrückt und unter Druck und Temperatur mit dem Interposer verpreßt und ausgehärtet. Die leitfähigen Partikel im Kleber stellen eine elektrische Verbindung in der Richtung von Bump zu Interposerpad (Z-Achse) her.

Bei Montage mit isotrop leitfähigem Kleber (Silberleitkleber) wird der Chip in den Kleber gedippt. Hier ist zu beachten, daß der Kleber nur die Bumps benetzt und keine Kurzschlüsse durch Klebstoffbrücken zwischen Bumps und Interposerpads entstehen. Die Aushärtung des Leitklebers erfolgt unter Druck und Temperatur. Nach dem Härten erfolgt eine Inspektion bzw. falls erforderlich Nacharbeit, daran schließt Underfilling an.

Zur Montage von Flip-Chips mit chemisch Ni/Au-Bumps wird die Vorbearbeitung der Wafer – Gold-Bumping und Vereinzelung – von Partnern durchgeführt. Das Waferbumping ist in der Regel nur bei größeren Serien sinnvoll. Die Verarbeitung dieser Flip-Chips kann in Klebetechnik durchgeführt werden.

Lotkugelpräparation (Balling)

Die Erzeugung der BGA- bzw. CSP-Lotkugeln auf den Interposern kann bei uns auf zwei Arten erfolgen. So können vorgefertigte Lotkugeln (Spheres) auf den Pads plaziert und per Reflow aufgeschmolzen werden. Die andere Möglichkeit besteht darin, per Schablonendruck die Lotpaste aufzubringen und diese anschließend aufzuschmelzen

Beim Interposer FC/PBGA-120/256 werden relativ große Kugeln mit einem Durchmesser von ca. 0,75 mm und einer Restkugelhöhe von 0,65 mm benötigt. Um die Kugeln per Schablonendruck aufzubringen, wäre aufgrund des großen Pastenvolumens eine sehr dicke Schablone erforderlich. Bei BGAs ist es aus diesem Grund vorteilhafter, vorgefertigte Lotkugeln zu verwenden. Das Aufbringen der Kugeln auf dem BGA-Interposer erfolgt bei Prototypen, Mustern und Kleinserien mit einer Schablone. Damit die Kugeln auf dem BGA haften, muß auf den Interposer zuvor etwas Lotpaste oder ein spezielles Flußmittel aufgebracht werden. Die positionierten Kugeln können dann aufgeschmolzen werden.

Der Interposer FC/CSP-172 weist den Pitch von 0,5 mm auf. Da bei kleineren Kugeln mit einem Durchmesser von 0,3 mm wesentlich weniger Pastenvolumen nötig ist, können die CSP-Kugeln per Schablonendruck aufgebracht werden. Hier muß darauf geachtet werden, daß das Verhältnis von Padöffnung zu Schablonendicke die nach IPC-Standard (J-STD-13) empfohlenen Werte nicht unterschreitet.

Eine andere Möglichkeit, Balling und Montage auf der Leiterplatte zu kombinieren, besteht in der Verwendung der BGA- bzw. CSP-Interposer FC/PBGA-120/256 bzw. FC/CSP-172 als Land-Grid-Array (LGA). Hier werden auf den Interposern keine Lotkugeln erzeugt, doch die Leiterplatte wird bedruckt und der Interposer in der Paste positioniert. Das bestückte Board durchläuft den Reflowofen. Diese Kugeln sind zwar relativ klein, da jedoch Interposer und Leiterplatte aus FR 4 bestehen, kommt es zu keinem Thermomismatch des Substrats, der Verbindungen schädigt. Generell gibt es drei unterschiedliche Möglichkeiten, die fertigen Interposer zu „verpacken“. Solch ein Gehäuse schützt bekanntlich das Bauteil (besonders ungehäuste Dies) vor mechanischen und chemischen Einflüssen. Bei Dam&Fill wird zuerst mit hochviskosem Material ein Damm zur Abgrenzung hergestellt. Er bildet die Außenkontur der Verkapselung und verhindert das Wegfließen des niederviskosen Füllmaterials, das im zweiten Schritt vollflächig aufgebracht wird. Materialien zur Aushärtung durch Wärme oder Bestrahlung mit UV-Licht sind verfügbar.

Als weitere Möglichkeit gibt es die Einkapselung der Chips per Siebdruck. Eine dicke Schablone, in die eine Kontur der Verkapselung eingeschnitten ist, wird mit Encapsulant-Material geflutet. An-schließend nimmt man die Schablone ab und härtet den Encapsulant. Die Spritzguß-Technik (Molding) hingegen ist die wirtschaftliche Lösung für große Stückzahlen. In einer Spritzgußmaschine werden die im Nutzen gefertigten BGAs oder CSPs in eine Form eingelegt und mit Kunststoff umspritzt.

Zuverlässigkeitsprüfungen

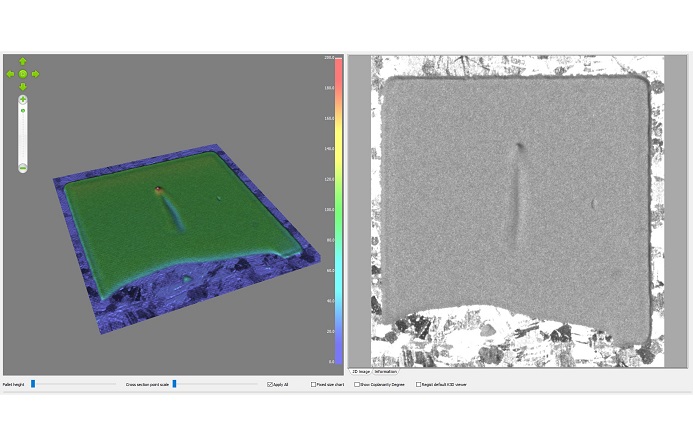

Das fertige Package auf dem Interposer kann zur Prüfung der elektrischen Kontaktierung und der Daisy-Chain-Verbindungen auf ein Board gesetzt werden, das seinerseits in das Future-Chip-Testboard zur Prüfung eingelegt wird. Nach dem Start des Tests zeigt eine Leuchtdiode für jede der 24 Daisy-Chain-Ketten an, ob die elektrische Verbindung in Ordnung oder unterbrochen ist. Werden Fehler festgestellt, kann das Modul durch Schliffbild (Bild 7) oder Röntgenuntersuchung analysiert werden.

Zur Bewertung der Packages in puncto Verbindungsqualität werden unterschiedliche Umgebungbedingungen simuliert (Tabelle 2). Dabei sind Zuverlässigkeitsaussagen auf Basis von Feuchtklima sowie mit normalen und erhöhten Temperaturen von besonderem Interesse. Genaue Widerstandsmessungen sowie Daisy-Chain-Kontrollen ermöglichen Aussagen zu De-gradationsmechanismen bei Feuchte und zu Fehlern. Derzeit wird im Rahmen eines vom BMBF geförderten Pojekts ein Meßplatz entwickelt, mit dem elektrische Charakteristika der Kontaktstellen während der Temperatursimulation on-line gemessen werden können. Mit den Testinterposern für BGAs und CSPs sowie dem Trainingskit für Einsteiger lassen sich Fertigungsprozesse für Advanced-Packages kostengünstig erproben und qualifizieren. Somit ist die Anwendung der Advanced-Packages nicht nur Großunternehmen mit starken Ressourcen vorbehalten, sondern auch kleinen und mittleren Unternehmen. Binder Elektronik hat 25 Jahre Erfahrung in Design und Fertigung von Baugruppen, wobei man vor sechs Jahren die BGA-Technik einführte. Inzwischen ist auch die Montage von Flip-Chips auf Leiterplatten, Flexschaltungen, Keramik und Glassubstraten möglich. Im Standard-SMD-Prozeß lassen sich Flip-Chips mit Solder-Bumps verarbeiten. Prototypen, kleine und mittlere Serien werden in Waldstetten gefertigt, für Großserien stehen Partner in USA und Asien zur Verfügung.

EPP 226

Unsere Webinar-Empfehlung

Applikationen aus dem Bereich der Leistungselektronik gewinnen immer mehr an Bedeutung. Die Inspektion dieser Applikation lässt sich mit der bewährten Standardtechnologie der 3D-Messtechnik bewerkstelligen.

Teilen: