Bei Lucent-Alcatel werden Chassis-Produkte getestet, die über eine Midplane mit insgesamt 42 Kartensteckplätzen verfügen. Eine Mid- plane ist eine Backplane, in die sich Karten von vorne und hinten einstecken lassen. In 34 dieser Steckplätze lassen sich unterschiedlichste Karten von verschiedenen Anbietern einstecken. Um zu überprüfen, ob alle Chassis-Steckplätze richtig funktionieren, werden normalerweise in alle Steckplätze Karten eingesteckt und dann ein spezieller „Steckplatz-Funktionstest“ durchgeführt.

Bill Philbrook, Lucent-Alcatel

Anschließend erfolgt dann als Ergänzung ein weiterer Test, bei dem das Chassis mit den für die Integration in die Kundenanlage vorgesehenen Karten bestückt wird. Dadurch lässt sich sicherstellen, dass die Karten die jeweiligen Spezifikationen erfüllen. Da die Testzeiten für die Überprüfung der Chassis relativ lang waren, diskutierte unser Team, wie diese auch von der Konfiguration abhängigen Zeiten reduziert werden könnten. Als mögliche Alternativen kam ein kommerziell verfügbarer Chassis-Tester mit speziell entwickelten Interface-Karten (Paddleboards) oder ein Boundary-Scan-Tester ebenfalls mit speziellen Paddleboards, über die die Verbindungen mit der Midplane hergestellt werden, in Betracht. Bei der ersten Lösung würden allerdings rund 20 000 Verbindungsleitungen zum Testen benötigt. Da wir bereits eine Boundary-Scan-„Test-Box“ für Tests auf Baugruppenebene im Einsatz hatten und diese nur ein Kabel mit fünf Signalleitungen benötigt, entschieden wir uns für diese Lösung. Der Boundary-Scan-Ansatz bot darüber hinaus noch weitere Vorteile, wie deutlich geringere Kosten, einen höheren Testdurchsatz und die Einfachheit. Zu den Nachteilen dieser Möglichkeit gehören unserer Ansicht nach die Notwendigkeit der Entwicklung und Unterstützung von Boundary-Scan-Tests sowie die Unsicherheit, ob die bestehende Boundary-Scan-Hardware und -Software für ein derart großes Projekt auch geeignet ist.

Da weder unsere Gruppe noch unser Midplane-Hersteller entsprechende Paddleboard-Tester verfügbar hatte und wir eine gewisse Herstellerunabhängigkeit erreichen wollten, fiel die Entscheidung für den Boundary-Scan-Ansatz leicht. Bevor wir mit dem Boundary-Scan-Design starteten, konsultierten wir die technische Unterstützungsgruppe von JTAG Technologies. Damit sollte sichergestellt werden, dass die bestehende Testgenerierungssoftware auch für unser geplantes Design mit insgesamt 42 Paddleboards und einer Midplane funktionieren würde. (Die bereits vorhandene Hardware und Software von JTAG Technologies sollte für dieses Projekt weiter genutzt werden.)

Paddleboard-Design

Die Midplane-Tests erforderten die Entwicklung von drei unterschiedlichen, von vorn eingesteckten Paddleboards und von zwei verschiedenen, von hinten eingesteckten Paddleboards, um eine vollständige Boundary-Scan-Testabdeckung für alle Steckplätze zu gewährleisten. Drei dieser fünf Designs beinhalteten zusätzliche Hardware, durch die das Paddleboard in verschiedenen Steckplätzen mit unterschiedlicher Steckerbelegung funktioniert. Obwohl die Steckverbinder vom jeweiligen Steckplatz der Karte abhängig sind, konnten wir die gleiche Schaltung auf allen Karten verwenden. Das Paddleboard, das die Verbindung zum externen Boundary-Scan-Tester herstellt, verfügt über eine externe 5-kanalige Schnittstelle mit einem DB-9-Steckverbinder auf der Frontplatte der Karte (Bild 1). Die in Bild 2 dargestellte Karte bietet ähnliche Funktionalität, wird aber in die Rückseite der Midplane eingesteckt.

Da bis zu 42 Testkarten für die Tests benötigt wurden, hat man sich für den Einsatz des 10-Bit-TAP-Transceivers (Test Access Controller) 74LVT8996 von Texas Instruments in die Scan-Chain-Designs entschieden. Um jeden einzelnen TAP-Transceiver adressieren zu können, wurden fünf an jedem Midplane-Steckplatz schon vorhandene Address-Leitungen verwendet. In den Kundensystemen werden diese Leitungen normalerweise zur Identifizierung der jeweiligen Steckplätze im Chassis genutzt. Um Störung zu reduzieren, enthält unser Design an der Schnittstelle zur Midplane zusätzliche Treiberbausteine für die Boundary-Scan-Signale.

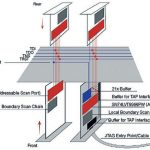

Die TMS-, TDI-, TRST- und TDO-Boundary-Scan-Signale sind über Steckverbinder mit jedem Kartensteckplatz auf der Midplane verbunden. Das Boundary-Scan-Eingangs-Paddleboard steckt allerdings in einem Steckplatz, der jedes Paar der vorderen/hinteren Karten mit einem separaten TCK-Taktsignal versorgt (Bild 3). Durch diesen Ansatz lassen sich die Störungen auf den TCK-Leitungen minimieren. Für die TCK-Verbindungen hätte man auch einen separaten Steckverbinder nutzen können, doch bei dieser Taktverteilung zeigten sich Signalintegritätsprobleme bei hohen Frequenzen.

Eine LED auf jedem Paddleboard zeigt die Übereinstimmung der Steckplatzadresse der Karte und der vom Boundary-Scan-Test zugeordneten Adresse. Diese LED hat sich besonders beim Debugging von Infrastrukturfehlern in defekten Einheiten bewährt. Damit lässt sich sehr einfach bestimmen, welche Karte der Tester gerade adressiert.

Nachdem die Paddleboard-Schaltungen fertig entwickelt und auch das Layout abgeschlossen war, wurde mit Hilfe der Softwarewerkzeuge von JTAG Technologies sichergestellt, dass die Netzlisten zusammenpassen und die Software die Infrastruktur- und Interconnect-Tests problemlos generieren kann. Zusammen mit dem Unternehmen wurden einige kleinere Probleme gelöst und der Testcase erfolgreich fertig gestellt.

Um die Hardware zu testen, wurde zuerst nur ein Paddleboard mit der Boundary-Scan-Schnittstelle gebaut. Diese Schaltung – die auf allen Paddle- board-Designs identisch ist – arbeitete fehlerfrei, so dass die weiteren vier Paddleboard-Designs implementiert werden konnten.

Vorläufige Tests

Um das Projekt zu vereinfachen, entwickelte man erste Boundary-Scan-Tests für die einzelnen Front-Karten und dann für jedes Paar der vorderen/hinteren Karten im Chassis. Für die 21 Tests, einer pro vorderer/hinterer Paddleboard-Kombination, mussten wir 21 Gruppen aus drei Netzlisten kombinieren, jeweils zwei für die Paddleboards und eine für die Midplane. Damit erhielten wir die notwendigen Netzlisten für jedes vordere/hintere Paar im Chassis. Nach einer gewissen Zeit funktionierten alle diese Kombinationen. Wir hatten meist kleinere Probleme zu identifizieren und zu beheben, die den Test und das Debugging stören konnten.

Nachdem der fehlerfreie Betrieb aller Paddle- boards verifiziert war, erfolgten die Erstellung und das Debugging der Kombinationen für die 42 Paddleboards und die Midplane. Dieser Prozess, einschließlich einer Wartezeit von vier Tagen bis der Testgenerator seinen Durchlauf abgeschlossen hatte, verlief problemlos. Erwartet war eigentlich eine längere Laufzeit, da bevor die Hardware fertig war, erste Versuche gestartet wurden. Für diese benötigte ein langsamerer Computer ungefähr sieben Tage.

Test des Systems

Um die Möglichkeit unserer Hardware und Software zu testen und um „Start-up“-Probleme frühzeitig erkennen zu können, bestückten wir ein Chassis mit einigen Karten und bauten einen Kurzschluss zwischen zwei Signalleitungen bzw. Knoten ein. Die ausgesuchten Knoten waren beide mit einem 3-Zellen-Boundary-Scan-I/O-Pin verbunden. Leider wurde der Kurzschluss beim Test nicht erkannt. Der Testgenerator hatte Testmuster erstellt, die zwar alle Knoten bei den einzelnen Testschritten ansteuerten. Aber durch die Entkopplung über die integrierten Serienabschlusswiderstände an allen Boundary-Scan-Pins war es möglich, am einen Knoten ein Logik-H-Pegel sowohl zu treiben als auch zu messen, während sich gleichzeitig am anderen kurzgeschlossenen Knoten ein Logik-L-Pegel treiben und messen ließ. Wenn mindestens einer der beiden kurzgeschlossenen Knoten zwei Boundary-Scan-fähige I/O-Pins gehabt hätte, wäre das Problem vom Tester entdeckt worden, da dann ein Pin am Knoten als Treiber arbeitet, während der andere Pin den Status des Knoten misst. So konnte kein Kurzschluss zwischen den beiden Knoten entdeckt werden, weil jeder mit nur mit einem einzigen Boundary-Scan-I/O-Pin verbunden war. Glücklicherweise verfügen beinahe alle Knoten in unserem System über mindestens zwei I/O-Pins, weil nahezu alle Pins über die Midplane mit den I/O-Pins sowohl auf dem vorderen als auch auf dem hinteren Paddleboard verbunden sind.

Die bei diesem Test verwendeten einzelnen I/O-Knoten gehen zu einem DB-9-Steckverbinder auf dem Paddleboard, den wir für eventuell notwendige externe Verbindungen nutzen wollten. Als ein weiterer Kurzschluss zwischen zwei Midplane-Leitungen mit zwei I/O-Pins auf jeder Leitung einbaut wurde, entdeckte der Test den Fehler und man erhielt eine korrekte Diagnose.

Bei einem weiteren Test verwendete man ein fehlerhaftes Chassis, das mit 42 fehlerfreien Karten bestückt war. Aber auch dieses fehlerhafte Chassis durchlief den Test ohne Fehler! Mittels „altmodischer“ Fehlersuchverfahren fand man einen Treiber-Knoten, bei dem die Spannung nicht auf den erwarteten Wert anstieg. Dieses Problem wurde durch einen 80-Ohm- Kurzschluss zwischen zwei Knoten auf der Midplane verursacht.

Die zwei bei diesem Fehler beteiligten Knoten hatten jeweils mehr als einen Treiber. Aber durch den hochohmigen Kurzschluss zwischen den Knoten konnte jeder Knoten noch problemlos den Treibern auf diesem Knoten folgen. Nach einigen Analysen beschloss man, manuell generierte Tests für jedes Paar der vorderen/hinteren Paddleboards durchzuführen. Die manuellen Tests sollten im Wesentlichen hochohmige Kurzschlüsse entdecken und würden auch an Knoten funktionieren, für die nur ein I/O-Pin vorgesehen war.

Da alle Boundary-Scan-Treiber über Pull-Up-Widerstände auf den Paddleboards verfügten, würden die neuen Tests nur ein paar Pins auf L treiben und die Widerstände würden die übrigen Pins nach oben ziehen. Die Tests würden niemals direkt benachbarte Steckverbinderpins auf L treiben, um sicherzustellen, dass Kurzschlüsse zwischen benachbarten Pins entdeckt werden könnten. (Ein Kurzschluss zwischen benachbarten Pins würde beide Pins auf L ziehen.)

Dieser Test funktionierte gut, so dass der vollständige Interconnect-Test für jedes einzelne vordere/hintere Paddleboard mit in den Gesamttestplan einbezogen wurde. Das Testsystem diagnostiziert jetzt problemlos andere Chassis-Fehler ohne manuellen Debug-Aufwand. Wir nutzen einen unserer Tester jetzt in einem Reparaturdepot. Ein weiterer Tester wird in der Fertigungseinrichtung eingesetzt, welche die Midplanes in die Chassis integriert.

Testzeiten

Die Testzeit eines Interconnect-Tests bei einem System mit 42 Paddleboards mit jeweils 500 bis 700 Verbindungen zur Midplane liegt bei ungefähr sechs Sekunden bei einem 1 MHz Takt oder bei zwei Sekunden bei einem 4 MHz Takt. Die Kurzschluss-Prüfungen dauern ungefähr zwei Sekunden (4 MHz) für jeden der 21 Steckplätze.

Die Gesamttestzeit für ein fehlerfreies Chassis beläuft sich auf weniger als eine Minute. Es dauert rund 10 bis 15 Minuten, um die 42 Karten zu installieren und das Boundary-Scan-Kabel anzuschließen. Unser Testsystem benötigt nur wenige Sekunden, um Infrastrukturfehler oder Fehler bei den 21 Kurzschlusstests zu finden und anzuzeigen – einen Test pro Paddleboard-Paar. Das gegenwärtige System, in dem ein älterer PC verwendet wird, braucht ungefähr 27 Minuten für den gesamten Interconnect-Test. Auf Grund der langen Testzeit wird der umfassende Interconnect-Test erst durchgeführt, wenn zuvor die nur wenige Sekunden dauernden Kurzschlusstests erfolgreich durchlaufen worden sind.

Die Boundary-Scan-Verfahren, die im Produktionstest und zum Debugging der Midplane verwendet werden, sind mit einem Test einer einzelnen Baugruppen vergleichbar. Somit können die Ingenieure und Techniker ihr bereits erworbenes Fachwissen und ihre Fertigkeiten auch beim Einsatz unseres neuen Testsystems nutzen. Nach den bisherigen Erfahrungen sollten wenn möglich eher schnellere und kleinere Tests eingesetzt werden. Dadurch müssen dann auch keine langen Diagnosezeiten mehr abgewartet werden.

EPP 468

Unsere Webinar-Empfehlung

Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine zeitnahe schnelle Messung…

Teilen:

.png)