Wegen der vielfältigen Natur der MEMS unterscheidet sich der Einbau von MEMS-Bauteilen von der IC-Gehäusung. Der MEMS-Einbau hat verschiedensten und breit gefächerten Anforderungen Rechnung zu tragen. Forderungen nach niedrigen Kosten und stärkerer Miniaturisierung treiben die Technologie zu kompakteren, auf dem Wafer ausgeführten Einbauverfahren, die sich für eine ganze Reihe von MEMS-Bauteilen eignen. Subsystem-Integration von MEMS-Bauteilen macht steigenden Gebrauch von modernen, kompakten Einbautechniken wie Chip-Stacking und Integration in Multi-Chip-Module.

Bei mikroelektromechanischen Systemen (MEMS) handelt es sich um miniaturisierte Systeme mit elektrischen und nichtelektrischen, z.B. mechanischen, optischen und biochemischen Komponenten. Für künftige intelligente Bauteile sind sie unentbehrliche Bestandteile, da sie neuartige Funktionen bieten oder Energie liefern können. Im Vergleich zur IC-Entwicklung sind bei ihnen die Zusammenhänge zwischen Technologie, Komponenten und Anwendung wesentlich komplexer. Concurrent-Engineering, das gleichzeitig Modellierung, Simulation, Technologie, Gehäuseeinbau und Zuverlässigkeit beachtet, ist daher von entscheidender Bedeutung.

Der Einbau von MEMS bestimmt ihr funktionelles Verhalten wie auch ihre Fertigungskosten. Ein MEMS-Gehäuse hat zunächst Anforderungen wie an ein IC-Gehäuse zu erfüllen, und dann noch zusätzliche Funktionen zu bieten, die meist von der Anwendung abhängen. Für kosteneffiziente Lösungen besteht noch die Zusatzforderung nach der Entwicklung von Einbauverfahren, die sich für ein breites Spektrum von MEMS-Bauteilen eignen. In diesem Artikel werden einige aktuelle Trends in MEMS-Einbaulösungen betrachtet, speziell im Bereich des Einbaus auf Wafer-Ebene WLP (wafer level packaging).

Was unterscheidet MEMS-Einbau von IC-Gehäusung?

Der Einbau von ICs dient hauptsächlich dazu, den Chip mechanisch zu stützen, elektrisch mit der Schaltung zu verbinden und so weit wie möglich von Umgebungseinflüssen zu isolieren. Auf der anderen Seite sind MEMS sehr oft eng mit ihrer Umgebung verbunden und von vielfältiger Natur. Als Konsequenz hat der Einbau von MEMS verschiedene und weiter reichende Anforderungen als die IC-Gehäusung zu erfüllen:

- MEMS sind nicht Miniaturisierungstrends wie ICs unterworfen, auch wenn es gelungen ist, bestimmte Strukturen zu verkleinern. MEMS arbeiten mit Energie als Eingangs- oder Ausgangsgröße; daher bringt eine Miniaturisierung keine vergleichbaren Vorteile wie für ICs.

- Bei MEMS gibt es eine große Vielfalt an grundlegenden Bausteinen: Sensoren und Aktoren können aus verschiedensten Elementen bestehen: pyroelektrische, resistive, thermoelektrische, magnetische, akustische, chemische, optische usw.

- Es gibt oft keinen vorherrschenden Prozessablauf für einen bestimmten Baustein.

- Die Einbau-Funktionalität ist breiter angelegt. IC-Gehäuse haben sich an die immer größere Dichte der elektrischen Ein-/Ausgangsanschlüsse und das steigende Niveau der elektrischen Verlustleistung und Entwärmung anzupassen. Umgebungsparameter, wie Feuchte oder Druck, werden als unerwünschte Störgrößen behandelt, gegen die das Chip durch ein Gehäuse vollständig abgeschottet werden soll. Beim Einbau von MEMS sind die elektrischen Ein-/Ausgänge eher unidirektional und weniger dicht. Das Thema elektrischer und thermischer Energie ist weniger interessant, aber mindestens eine der nichtelektrischen Einflussgrößen wird beispielsweise beim Sensor zum gewünschten Eingangssignal.

Wegen der zusätzlichen Anforderungen an den Einbau lässt sich die Klassifikation der herkömmlichen IC-Gehäusung in vier hierarchischen Ebenen weniger auf MEMS anwenden. Während die Ebene 0 bei ICs die Verbindung der zahlreichen Transistoren, Gatter oder Zellen auf dem Chip selber (also Operation auf dem Wafer) umfasst, werden unter Ebene 0 des Einbaus von MEMS auf Wafer-Ebene alle Verarbeitungsschritte auf Wafer-Ebene (z.B. Operationen, an denen mindestens ein voller Wafer beteiligt ist) verstanden. Die Einbauschritte der Ebene 1 finden statt, nachdem die einzelnen MEMS-Bauteile und ICs dem Wafer entnommen wurden.

Einbautrends bei MEMS

Da sie weniger allgemeiner Natur sind, werden MEMS-Prozesse vermutlich niemals das hohe Maß an Standardisierung wie CMOS-Prozesse erreichen. Entwicklungspläne (roadmaps) für das Wafer-Verarbeiten und den Einbau von MEMS werden deshalb weniger ausgereift und aussagekräftig sein als ihre IC-Gegenstücke. Dennoch lassen sich vier Trends für Einbau und Integration von Subsystemen herleiten, die auf den beiden treibenden Kräften der gegenwärtigen MEMS-Entwicklung basieren: Kostenreduzierung und Miniaturisierung.

- Integrations- und Gehäusekonzepte für kompaktere hybride IC plus MEMS,

- steigende Anwendung von Dünnfilm, Gehäusung auf Wafer-Ebene und Systemintegrationskonzepte,

- wachsende Synergien zwischen Ausrüstungen für MEMS-Fertigungskonzepte und IC/MEMS-Gehäusung sowie

- Trend zu Niedertemperaturtechnologien, die sich auf eine Vielfalt von Substraten anwenden lassen, wie IC-Wafer, Glas und Laminate.

Im nächsten Abschnitt werden diese Trends an einigen Beispielen von Gehäusekonzepten verdeutlicht, wie sie derzeit gebräuchlich sind. Diese Konzepte und ihr langfristiges Potenzial für den Einbau von MEMS werden näher betrachtet.

Einbaukonzepte der Ebene 0

MEMS in Wafer-Form sind allgemein sehr empfindlich gegenüber Umgebungseinflüssen, bis sie eingebaut sind. Sie enthalten nämlich oft fragile Teile, die während der Backend-Operationen, wie Sägen zum Vereinzeln, Pick-and-Place, Drahtbonden und Löten oder durch Einwirkung von Teilchen, beschädigt werden können. Daher ist ihr Schutz in einer frühen Stufe des Einbaus erforderlich. Das bedeutet, dass ein Einbau innerhalb der Ebene 0 (und/oder der Ebene 1) oft eine Abdeckfunktion des MEMS vorsieht. Diese Kapselung kann dann zusätzlich als strukturelles Teil für diejenigen MEMS dienen, die im Vakuum, bei niedrigem Druck oder in einer Schutzgasatmosphäre arbeiten. Für bestimmte Bauteile, wie Mikro-Relais oder Mikro-Beschleunigungsmesser, kann die Füllung der Kammer, die das MEMS umschließt, eine sehr wichtige Rolle beim Einstellen der Betriebseigenschaften spielen. Darüber hinaus ist offensichtlich, dass der Einfluss des Entstehungsprozesses der Kammer auf die Leistungsmerkmale des Bauteils auf ein Minimum reduziert werden muss. Dies erfordert dann eine Verarbeitung bei möglichst niedrigen Temperaturen und die Vermeidung des Einsatzes aggressiver oder korrodierender Stoffe während der Versiegelung. Natürlich müssen die Fertigungskosten so weit wie möglich reduziert werden, da der Einbau in ein Gehäuse einen bestimmenden Faktor der Herstellkosten von MEMS darstellt.

Drei Ansätze zur Gestaltung der Kapselung sind derzeit in Gebrauch: Bonden von Wafer auf Wafer, Bonden von Chips auf Wafer und Oberflächen-Mikrobearbeitungstechniken. Der generelle Ansatz beim Wafer-Wafer-Bonden sieht das Abdecken des einen Wafer, der die MEMS-Strukturen trägt, mit einem separaten, mikrobearbeiteten Wafer, in das ein kleiner Hohlraum eingearbeitet wurde oder das mit einem Distanzring versehen ist. Auf diese Weise lässt sich ein Wafer-Stapel aufbauen. Für das Bonden der Wafer gibt es mehrere Möglichkeiten, von denen das anodische Verfahren, Verschmelzen oder Glasschmelzen als bevorzugte Techniken gelten. Dabei bestimmen Prozess und eingesetzte Materialien die Dichtigkeit der Kammer und die Steuerbarkeit des Kammerinhalts. Dieser Ansatz ist gut etabliert und passende Ausrüstung mit hohem Durchsatz und guter Ausbeute kommerziell verfügbar. Als Hauptnachteil dieser Methode gelten die zusätzlichen Prozessschritte für den Zugang zu Bond-Flächen, die begrenzte Topologie, die für durchlaufende Signalleitungen erlaubt ist und – speziell im Falle des Schmelz-Bondens – die hohen Prozesstemperaturen. Allerdings versprechen neuere Entwicklungen mit Polymer-Verschlussmaterialien und Wafer-Verflachung eine Überwindung dieser Beschränkungen.

Das Bonden von Chips auf einen Wafer bietet eine wettbewerbsfähige Alternative. Vorbereitete und vereinzelte Abdeckungen werden mit einem Flip-Chip-Bonder nacheinander auf jedes MEMS-Bauteil platziert. Speziell für größere Chips ist dieser Ansatz wirtschaftlicher als das Bonden von Wafer auf Wafer. Für größere Chips wird nämlich die längere Bond-Zeit wegen der Montage einzelner Chips durch die Tatsache aufgewogen, dass die Bond-Flächen leicht zugänglich sind. Diese Technik lässt sich mit Niedertemperatur-Verschlussmaterial, einschließlich Lotverschluss mit Durchlässigkeiten unter 10–11 mbarl/s wie auch für dünne Abdeckungen einsetzen. Einen kostengünstigeren Weg zur Steuerung des Kammerinhalts bietet die Indent-Reflow-Sealing-Technik (IRS) von IMEC. Dieses Verfahren basiert auf dem Wafer-Bonden, bei dem Chips mit Lot-Bond überkopf (Flip-Chip) montiert werden. Eine optionale Abstandslage wird unterhalb der Lot-Lage implementiert, um die Höhe der entstehenden Kammer besser steuern zu können. Entscheidende Schritte der IRS-Technik sind: Erzeugung einer kleinen Füllöffnung, Plasma-Vorbehandlung zur Reinigung der Kammer, Pre-Bonden ohne Verschluss der Öffnung und abschließender Verschluss der Füllöffnung während des Reflow-Lötens in einem speziellen Ofen. Diese Methode bietet sowohl gute Dichtigkeit des Kammerverschlusses als auch Steuerbarkeit der Kam- merfüllung, zwei Eigenschaften, die für den Einbau von MEMS von besonderer Bedeutung sind. Darüber hinaus bietet diese Technik gute Möglichkeiten für den Einbau von MEMS-Bauteilen, die hohe Flexibilität im Hinblick auf Schutzgaszusammensetzung und Gasdruck erfordern. Zu den weiteren Vorteilen von IRS gehören niedrige Bond-Temperaturen von 220 bis 350 ºC. Da sich eine große Anzahl von Chips auf dem Wafer (oder Chip auf Chip) gleichzeitig verschließen lassen, ist diese Methode billig und liefert einen hohen Durchsatz.

Die kompakteste Art eines hermetischen Abschlusses nutzt Dünnfilm-Abdeckungen, die durch Oberflächen-Mikrobearbeitung entstehen. Bei diesem Ansatz enthält die Kammer einen Zugangskanal für das Ätzmittel der zu entfernenden Schicht. Nach Abschluss der Ätzung wird der Kanal geschlossen, und damit die Kammer versiegelt. Das Verschließen des Kanals erfolgt bequem durch reaktive Versiegelungstechniken, z.B. durch Aufbringen einer angepassten LPCVD-Schicht oder einfach durch Zudecken der Öffnung. Im Vergleich zu den anderen Ansätzen lassen sich die horizontalen Abmessungen der Abdeckung bis auf die Fläche des darunter liegenden MEMS-Bauteils verringern, wobei die Stärke der Abdeckung unter 50 µm liegen kann.

Diese Technik ist am komplexesten, bietet aber den entscheidenden Vorteil, dass sich eine ganze Reihe von Wafern gleichzeitig versiegeln lassen. Dabei hängen die Auswahl des Abdeckmaterials und der wegzuätzenden Schicht in gewissem Maße von dem darunter liegenden MEMS-Bauteil ab, was relativ hohe einmalige Entwicklungskosten verursacht. Bei der Massenproduktion von MEMS-Bauteilen kann der höhere Entwicklungsaufwand durch niedrigere Fertigungskosten aufgrund weitgehender Verarbeitung auf Wafer-Ebene und Einsparung von MEMS-Fläche ausgeglichen werden.

Integration von Subsystemen

Die Methoden des MEMS-Einbaus sind nicht auf den Einbau einzelner MEMS beschränkt. Ihre Anwendbarkeit umfasst auch die Integration von MEMS in Systeme. Die Integration von Subsystemen lässt sich natürlich in vielen Fällen durch herkömmliches Drahtbonden und Einbau in ein Standardgehäuse ausführen. Aber immer mehr kompakte Einbauverfahren, wie Chip-Stacking und Integration in Multi-Chip-Module werden für komplexe MEMS-Anforderungen entwickelt. Chip- Stacking wird angewandt für die Verbindung hochdichter Bildaufnehmer, Displays oder Tintenstrahler mit 100.000 Pixeln, mit ihren Adressier-und Auslese-ASICs. Hochfrequente MEMS-Bauteile, wie Schalter und Resonatoren, werden gemeinsam mit passiven HF-Komponenten in mehrlagige Dünnfilm-Module (MCM-D) integriert, was komplette HF-Systeme im Gehäuse ergibt. Diese MCM- D-Komponenten werden durch die Ablagerung von Dünnfilmmaterial und Dielektrika als Polymere oder anorganische Isolatoren, auf maßhaltigen Basismaterialien, wie Silizium, Glas oder Keramik, aufgebaut. Dabei gestattet die MCM-D-Technologie eine Integration von passiven Komponenten in das Substrat oder ihre Assemblierung in diskreter Form auf dem Substrat. Die Übertragung der HF-MEMS-Technologie auf eine MCM-D- Plattform erlaubt die Optimierung der Leistungsmerkmale von HF-Schaltern und Varicaps. Auf die gleiche Weise lassen sich auch andere Komponenten in eine derartige Plattform integrieren.

EPP 502

Unsere Webinar-Empfehlung

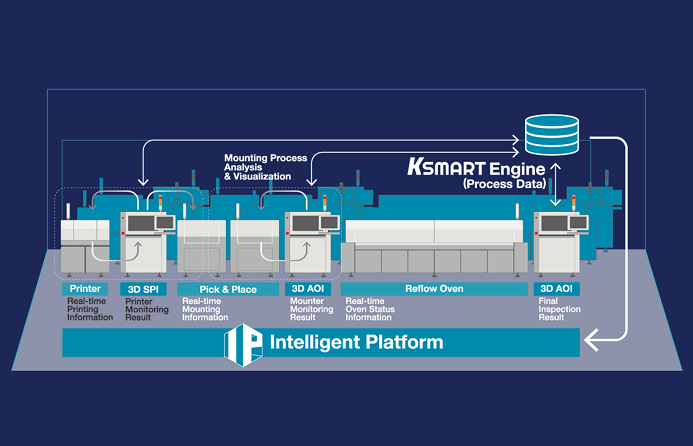

Die Nutzung der 3D-Mess- und Prozessdaten bringt die Produktionssteuerung auf die nächste Stufe. Echte 3D-Messung ermöglicht KI-basierte Prozessmodellierung zur Vorhersage von Parameteränderungen und -defekten oder zur Ursachenanalyse bis hin zu einzelnen Werkzeugen und Best…

Teilen: