Die Elektronikproduktion steht kurz davor, nach Europa zurückzukehren. Ausschlaggebend für diese Entwicklung ist der hohe Automatisierungsgrad in den Bereichen Bestückung (Assembly) und Test, welcher die Wirtschaftlichkeit bei der Produktion von Elektronikprodukten verbessert und Produktionsabläufe weitaus weniger arbeitsintensiv gestaltet. Durch die Verlagerung der Produktion näher an die Heimatmärkte, reduzieren sich auch die Frachtkosten sowie die zum Transport der Endprodukte erforderliche Zeit. Auch dies senkt die Kosten und erhöht die Effizienz.

Peter van den Eijnden, JTAG Technologies, Eindhoven (Nl)

Das ultimative Ziel eines EMS-Dienstleisters (Electronics Manufacturing Service) besteht darin, bestückte Leiterplatten zu liefern, die frei von Produktionsfehlern sind.

EMS-Dienstleister müssen normalerweise bei jedem Boardtyp mit einer großen Vielfalt an Produkten in kleinen Stückzahlen umgehen können. Als Folge daraus werden viele verschiedene Boardtypen auf der gleichen Fertigungsstraße hergestellt. Dies stellt die EMS-Dienstleister beim Streben nach ihrem Ziel „Null Fertigungsfehler“ vor eine zusätzliche Herausforderung.

Da Fertigungsfehler stets vorhanden sind, müssen Tests durchgeführt werden, um sie zu finden und zu beheben. Damit die Reparaturkosten niedrig bleiben, ist es entscheidend, die Möglichkeit, dass Fehler entstehen, zu reduzieren. So lassen sich die Fehlerabdeckung maximieren und Fehler zu einem frühen Zeitpunkt schnellstmöglich exakt aufspüren.

Reduzierung von Fertigungsfehler

Eine minimale Zahl von Fertigungsfehlern lässt sich mit einem hochwertigen Bestückungsprozess erreichen. Zudem genutzt werden DfM-Regeln (Design for Manufacturing). Auch wird der Umfang manueller Arbeiten minimiert (Full Reflow). Qualitativ hochwertiges Bestückungsequipment in Verbindung mit einer strengen Prozesskontrolle minimiert die Möglichkeit, dass Fertigungsfehler entstehen. Kurz – die DPMOs (Defects per Million Opportunities) werden minimiert.

Indem man die Durchführbarkeit der Bestückung einer Leiterplatte während der Entwicklungsphase prüft und, falls erforderlich, korrigiert, wird das physikalische Board-Design am besten an die Fähigkeiten der Bestückungslinie angepasst. So lässt sich die Möglichkeit von Fertigungsfehlern verringern. Durch die Kombination des DfM-Konzepts mit SMD-Bauteilen eignen sich Leiterplatten für das Full-Reflow-Verfahren mit wesentlich geringerem manuellen Arbeitsaufwand. Alle Maßnahmen zusammen resultieren in einer maximalen „First Pass“ Produktionsausbeute und bringen somit eine minimale Zahl an Reparaturen mit sich. Eine um y% verbesserte Produktionsausbeute bedeutet, dass y% weniger Boards repariert werden müssen.

Hohe Fehlerabdeckung, minimale Diagnosezeit

Durch die Optimierung des Bestückungsprozesses ergibt sich eine minimale Zahl an Fertigungsfehlern und somit eine minimale Zahl an Reparaturen. Zusätzlich minimiert ein Testkonzept zum Erkennen von Fertigungsfehlern, das die sofortige Lokalisierung von Fehlern ermöglicht, die Reparaturkosten pro Leiterplatte. Das Aufspüren aller möglicher Fehler ist normalerweise nicht durchführbar. Boards mit einem oder mehr als einem nicht aufspürbaren Fehler gelangen in die nächste Phase (Slip through). Um so etwas zu vermeiden, sollte das Testkonzept eine maximale Fehlerabdeckung aufweisen. Mit den richtigen Testmethoden und der Anwendung von DfT (Design for Test) lassen sich eine maximale Fehlerabdeckung erreichen und Defekte kosteneffizient lokalisieren.

Strukturtests konzentrieren sich auf die Aufspürung von Fertigungsfehlern. Diese Testmethode ermöglicht unmittelbare Diagnosen auf Pin-Ebene. Sie erfordert keine manuelle Fehlerbehebung (Troubleshooting) und minimiert somit die Arbeits- und Diagnosezeit. Strukturtests umfassen „visuelle“ Inspektionsmethoden (manuell oder automatisiert) und spezielle elektrische Testmethoden.

Mixed-Signal Boundary-Scan I/O reduziert Testkosten

Der JTAG Boundary-Scan bietet solche Strukturtestmethoden zu niedrigsten Kosten. Hinzu kommt, dass beim Einsatz von SMDs der Boundary-Scan die einzige Möglichkeit ist, um Zugang zu den Anschlüssen zu erhalten – speziell zum Beispiel bei BGA-Gehäusen (Ball Grid Array). Für den Boundary-Scan ist nur eine minimale Zahl an Probes erforderlich. Außerdem ist der Einsatz von Low-Cost Vorrichtungen (Fixtures) möglich, was die Testkosten weiter senkt.

Durch die Kombination von Mixed-Signal Testfähigkeiten mit Boundary-Scan Tests ist ein Strukturtest von Boards ausreichend, um Fertigungsfehler zu entdecken und den Ausschuss zu minimieren. Weitaus teurere Funktionstests zum Auffinden von Fertigungsfehlern auf Board-Ebene werden jetzt minimiert oder sind nicht mehr erforderlich.

Beim JT 5705 / USB handelt es sich um einen Mixed-Signal Boundary-Scan I/O-Controller, der über analoge und digitale Testfunktionen in Kombination mit Boundary-Scan-Funktionen verfügt. Diese Mixed-Signal Fähigkeiten bieten eine höhere Fehlerabdeckung als ein Standard-Boundary-Scan. Der Einsatz des Controllers in Verbindung mit einer speziellen Vorrichtung ermöglicht die einfache Handhabung in der Produktion.

Tbp electronics, ein niederländischer EMS-Dienstleister befestigte einen JT 5705 auf einem Spezial-Trägerboard innerhalb einer Vorrichtung, um eine kompakte Testkonfiguration zu realisieren. Mit Hilfe des DfM-Konzepts konnte tbp electronics die fehlerfreie Ausbeute beim ersten Durchlauf bei einem bestimmten Board um 20% auf fast 93% steigern. Durch den Einsatz des Mixed-Signal Boundary-Scan I/O-Controllers zum Testen der Leiterplatten wurde eine Fehlerabdeckung von über 97% und ein „Slip“-Wert von unter 0,2% erreicht.

Schlussbemerkungen

- Indem man das DfM-Konzept im Feld anwendet, steigt die Ausbeute. Als Folge sind weniger Reparaturen erforderlich.

- Durch das DfT-Konzept wird die Fehlerabdeckung von Strukturtests maximiert. Eine manuelle Fehlerbehebung ist nicht erforderlich. Daraus resultieren minimale Reparaturkosten pro Board.

- Indem man Mixed-Signal Testfähigkeiten mit Boundary-Scan kombiniert, ist ein Strukturtest von Boards ausreichend, um Fertigungsfehler aufzuspüren und den „Slip“ bei wesentlich geringeren Arbeitskosten zu minimieren. Auf weitaus teurere Funktionstests zum Aufspüren von Fertigungsfehlern auf einzelnen Boards kann oft oder ganz verzichtet werden. Daraus ergeben sich wesentlich niedrigere Entwicklungskosten für Test und Vorrichtungen.

electronica, Stand A1-221

Peter van den Eijnden ist Geschäftsführer von JTAG Technologies in Eindhoven. Das 1993 gegründete Unternehmen beschäftigt weltweit 60 Mitarbeiter. In der Firmenzentrale in Eindhoven arbeiten 30 Angestellte. Die restlichen Mitarbeiter sind in verschiedenen Verkaufs- und Kundendienstorganisationen in mehreren europäischen Ländern, den USA und China tätig. Das Unternehmen entwirft, produziert und verkauft Geräte für Boundary Scan Anwendungen. Mit diesen Geräten können Leiterplatten, unabhängig von den Anwendungsbereichen für die sie entwickelt wurden, auf universelle Weise getestet und konfiguriert werden.

Peter van den Eijnden hat 1981 an der TU Eindhoven seinen Studienabschluss im Fach Elektrotechnik/Digitale Systeme gemacht. Nach seinem Studium hat er als wissenschaftlicher Mitarbeiter an der TU Eindhoven und als Dozent für die neue Gymnasiallehrerausbildung, einige Jahre zu den Themen Mikroprozessoren, theoretische Schalttechnik sowie Entwurf von programmierbaren logischen Schaltungen und ASICs geforscht und gelehrt.

Von 1985 bis 1993 arbeitete er bei Philips Test- und Messgeräte. Er war an der Entwicklung von ASICs und Mikroprozessoremulatoren beteiligt, wurde anschließend Projektleiter für Logikanalysatoren und Boundary-Scan Anwendungen und später Leiter der Entwicklungsabteilung dieser Gruppe.

Unsere Webinar-Empfehlung

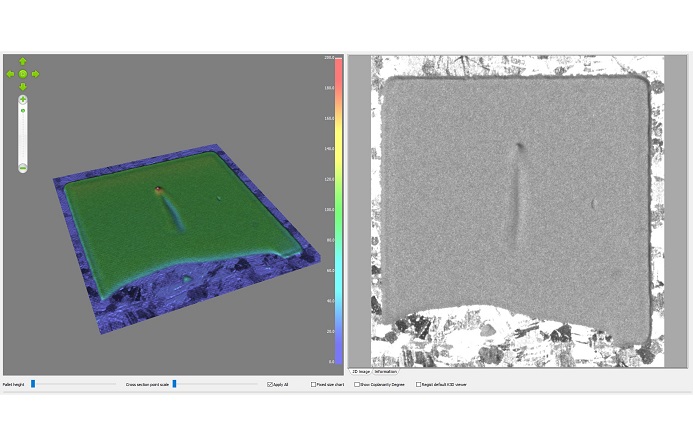

Applikationen aus dem Bereich der Leistungselektronik gewinnen immer mehr an Bedeutung. Die Inspektion dieser Applikation lässt sich mit der bewährten Standardtechnologie der 3D-Messtechnik bewerkstelligen.

Teilen: