Bleifrei-Implementierungen stellen neue Herausforderungen für die Leiterplattenproduktion hinsichtlich Design, Lötprozess und Qualitätssicherung dar. Die höheren Reflow-Prozesstemperaturen führen zu höheren thermischen Belastungen sowohl beim Leiterplatten-Substrat als auch bei den Bauteilen. Das engere Lötprozessfenster, das zwischen dem höheren Schmelzpunkt des bleifreien Lotes und der maximal zulässigen Bauteiltemperatur liegt, macht den Lötprozess erheblich diffiziler. Um das erforderliche DPM-Niveau und minimale Baugruppenausfälle zu gewährleisten, müssen spezifische Voraussetzungen erfüllt werden.

Mark Cannon und Jürgen Friedrich, ERSA, Wertheim

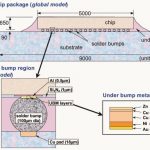

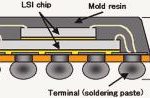

Insbesondere die sehr kleinen Lötverbindungen von Flip Chips (FCs) und Chip Scale Packages (CSPs) sind beim bleifreien Löten hohen thermischen Belastungen ausgesetzt, die zu folgenschweren Defekten führen können. Der interne Aufbau von FCs und CSPs ist von Hersteller zu Hersteller stark unterschiedlich. Zwei abweichende interne Designs sind in den Bildern 1 und 2 dargestellt.

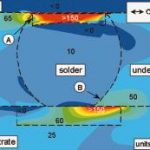

Die extrem kleinen Bauteilanschlüsse von FCs bzw. CSPs sind bei mechanischer Belastung einem höheren Ausfallrisiko unterworfen. Zum besseren Verständnis der Fehlermechanismen haben Professor Toshio Nakamura und Gary Yu Gu umfangreiche Untersuchungen durchgeführt, indem sie wahrscheinliche Bruchsituationen und potenzielle Delaminierungsstellen bei Flip Chip Bauteilen getestet haben. Ihre Arbeit mit dem Titel „Mechanical Behaviors of Flip-Chip Packaging“ (Mechanisches Verhalten von Flip-Chip Bauteilen) zeigt deutlich, dass gehäuseseitige Lötverbindungen einem höheren Delaminierungsrisiko unterworfen sind (Bild 3 und 4).

In der Publikation „Mechanical Reliability of Underfilled CSP Assemblies“ (Mechanische Stabilität von Underfilled CSP-Bauteilen“) von Murtuza Rampurawala, Michael Meilunas, und Arun Gowda & K. Srihari, Ph.D., machen die Autoren auf das Problem der gehäuseseitigen Delaminierung von CSP-Anschlüssen aufmerksam:

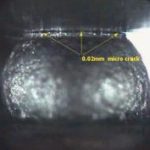

Durch Querschnittsanalysen fehlerhafter Bauteile konnten Risse in der Lötverbindung entlang der Gehäuseoberfläche der Bauteile festgestellt werden. Bild 5 zeigt eine Aufnahme des Bauteils H (ohne Underfill) das bei einem Torsionstest ausgefallen ist. Der Riss entstand an der Berührungsstelle von Lötmaske und Bauteilanschluss. Bild 6 zeigt einen Querschnitt des Bauteils D, Underfill mit UF1, das nach 1825 Torsionszyklen ausgefallen ist.

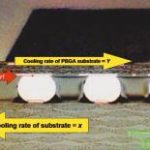

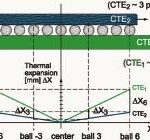

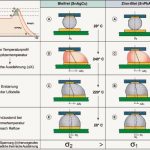

Bei FCs und einigen CSPs wird die mechanische Stabilität durch Underfill nach dem Löten verstärkt. Falls vor dem Underfill-Prozess Delaminierungen auftreten, die nicht erkannt werden, führt dies zu einem vorzeitigen Ausfall im Betrieb. Viele Area Array Packages, inklusive CSPs, verwenden einen Interposer zum Ausgleich der internen Spannung in den Lötverbindungen, die durch verschiedene Wärmeausdehnungskoeffizienten (CTE) während des Aufheiz- und Abkühlprozesses entsteht. Das grundlegende Problem verschiedener CTEs ist in Bild 7 dargestellt. Durch die Tatsache, dass die CTEs des Leiterplattensubstrats und des Bauteilkörpers unterschiedlich sind, entsteht eine relative Bewegungsdifferenz zwischen den sich ausdehnenden Materialien. Diese steigt mit höheren Prozesstemperaturen noch an. Während der Abkühlung entsteht wieder eine relative Bewegungsdifferenz zwischen den sich zusammenziehenden Materialien, die bis zum Abscheren führen kann.

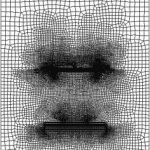

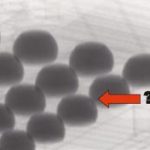

Bild 8 zeigt die Tatsache, dass die Bewegung an den Ecken des Bauteils größer ist. Betrachtet man die Mitte des Bauteils als Nullpunkt, ist die relative Bewegung der mittleren Kugel gleich „0“. Je weiter man in Richtung der Ecken des Bauteils kommt, desto größer wird die relative Ausdehnungsdifferenz, bezogen auf den Bauteilmittelpunkt. Beispielsweise ist der Unterschied bei Kugel 6 (DX6), größer als bei Kugel 3 (DX3). Während des Abkühlens ziehen sich die Materialien wieder zusammen, und die relative Ausdehnungsdifferenz zwischen der Leiterplatte und dem Bauteil wird durch das Erstarren des Lots „eingefroren“. Da alle Materialien bei Raumtemperatur wieder ihre Ursprungsposition anstreben, verbleibt damit eine gewisse Scherspannung in der Lötverbindung. Diese Spannung ist an den Ecken des Bauteils erheblich größer und kann zur Bildung feiner Risse führen. Aus diesem Grund ist es entscheidend, dass Leiterplatten-Entwickler die richtigen Materialpaarungen hinsichtlich der verschiedenen Wärmeausdehnungskoeffizienten wählen.

In ihrer Forschungsarbeit „3D Interfacial Delamination Near Solder Bumps in Flip Chip Package“ (3D-Delaminierung an Lötkontakten bei Flip Chip Bauteilen) haben die Autoren Yu Gu und Toshio Nakamura das Problem der höheren Belastung an den Bauteilecken herausgestellt. Bild 9 verdeutlicht, dass die Scherbelastung von der Mitte zu den Kanten ansteigt, und dass der Flächenversatz an den Bauteilkanten höher ist.

Eine Analyse, wie sich die höhere Belastung der Kugeln an den Ecken von Area Array Packages insbesondere beim Bleifreiprozess auswirkt, findet sich in der Publikation „HDPUGs Failure Analysis of High-Density Packages Lead-Free Solder Joints“ (HDPUGs Fehleranalyse von Bleifrei-Lötverbindungen bei High-Density Packages).

Es kann beobachtet werden, dass sich das Bauteil durch die höheren Bleifrei-Reflowtemperaturen erheblich verformt. Dies führt zu unregelmäßig geformten Lötverbindungen an den Ecken und dicker geformten Lötverbindungen in der Mitte. Die fehlerhaften Lötverbindungen des Bauteils liegen an den Ecken der äußeren Kugelreihen. Dies ist auf die Wärmeausdehnungsunterschiede zwischen dem Bauteil und der Leiterplatte zurückzuführen.

Wodurch steigt das Risiko von fehlerhaften Lötverbindungen beim Bleifreilöten?

Die oben beschriebenen grundlegenden Probleme von FC- und CSP-Lötverbindungen werden bei Bleifreiprozessen durch drei entscheidende Faktoren verstärkt: 1. die Prozesstemperaturen bei Bleifrei sind höher, 2. die Erstarrungstemperatur von bleifreien Lötverbindungen liegt erheblich höher und näher an der Peak-Reflowtemperatur als bei SnPb-Lot, und 3. die unterschiedlichen Ausdehnungen werden bei höheren Temperaturen noch verstärkt. In Bild 10 wird die Problematik verdeutlicht.

Die Startbedingungen beider Prozesse sind bei Raumtemperatur (A) identisch. Beim Aufheizen der Baugruppe ist die relative Ausdehnungsdifferenz (DX3) beim Bleifreiprozess durch die höhere Peaktemperatur (D) stärker als die relative Ausdehnung (DX2) bei Zinn-Bleiprozessen mit ihrer niedrigeren Peaktemperatur (C). An Punkt (C) des Temperaturprofils erstarrt das Bleifreilot bereits an Position DX2, wobei im Vergleich das Zinn-Blei Lot noch flüssig ist. Die Materialkontraktion beim Zinn-Blei Prozess findet in einem längeren flüssigen bzw. flexiblen Zustand statt. Das Material kann deshalb bis zur Position (DX1) am Erstarrungspunkt der Balls (B) zurückwandern. Da alle Materialien bei Raumtemperatur (E) wieder ihre Ausgangsposition (X0) einnehmen, ist die verbleibende Scherbelastung (s2) bei Bleifrei-Lötverbindungen größer als bei Zinn-Blei Verbindungen (s1). Es sollte beachtet werden, dass es schon bei einem Reflowzyklus durch die verbleibende Belastung (s) zum Abscheren oder Delaminieren kommen kann. Über geeignete Inspektionstechniken müssen solche Fehler erkannt und korrigiert werden, bevor es zu kostenintensiven Feldausfällen kommen kann. Im Reflowprozess kann die Kontraktionsdifferenz über die Einstellung der Kühlluftverteilung zwischen LP Ober- und Unterseite beeinflusst werden.

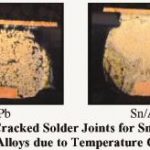

In der Publikation „Reliability of Lead-Free Solder Connections for Area-Array Packages“ (Zuverlässigkeit von Bleifrei-Lötverbindungen bei Area-Array Packages) von Ahmer Syed, Amkor Technology, Inc. unterstreicht der Autor das Delaminierungsproblem an der Bauteilseite, das beim Bleifreilöten besteht: Die eingangs beschriebenen Fehler wurden mittels Dye-and-Pry- und Querschliffen ermittelt. Insgesamt lässt sich sagen, dass die fehlerhaften Lötverbindungen bei all diesen Bleifreiloten auf der Gehäuseseite aufgetreten sind, genauso wie bei SnPb-Legierungen. Ein Querschliff der Verbindungen mit SnPb- und SnAgCu-Legierungen ist in Bild 11 dargestellt.

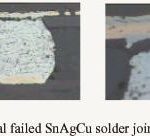

In seiner aktuelleren Publikation „Accumulated Creep Strain and Energy Density Based Thermal Fatigue Life Prediction Models for SnAgCu Solder Joints“ hat Ahmer Syed dieses Problem nochmals unterstrichen: In allen hier dargestellten Fällen haben die Lötverbindungen gehäuseseitig versagt. Bild 12 zeigt einen typischen Querschnitt einer defekten Lötverbindung mit einem Riss nahe der intermetallischen Zone der Gehäuseseite.

Zusammenfassend lässt sich sagen, dass durch unterschiedliche Wärmeausdehnung die Eckverbindungen von Area Array Packages höheren Belastungen ausgesetzt sind. Daher ist es klar, dass der Bleifreiprozess bei FCs und CSPs ein erheblich höheres Risiko hinsichtlich der gehäuseseitigen Delaminierung von Lötkugeln birgt. Die Auszüge aus den oben genannten Fachpublikationen untermauern die Problematik der gehäuseseitigen Delaminierung bei verschiedenen FC- und CSP-Bauteilen. Sowohl beim Leiterplatten-Design als auch während der Produktion muss noch sorgfältiger vorgegangen werden, um dieses Problem zu minimieren. Entscheidend ist die Einführung von Inspektionsmethoden für die Nullserie, um diese gravierende Fehler zu erkennen, bevor es zu kostenintensiven Feldausfällen kommt.

Inspektionssysteme für eine zerstörungsfreie Erkennung

Area Array Packages im Allgemeinen und FC- sowie CSP-Bauteile im Speziellen stellen Inspektionssysteme vor erhebliche Herausforderungen. Problematisch ist schlichtweg die Tatsache, dass die Lötverbindungen extrem klein sind und versteckt unter dem Gehäuse liegen. Querschliffe dieser Bauteile anzufertigen ist zeit- und kostenaufwändig. Sie liefern jedoch die erforderlichen Ausfallanalysedaten, die zum Verständnis und zur Korrektur von Prozess- oder Materialproblemen notwendig sind. Diese zerstörende Methode kann allerdings nicht bei allen Leiterplatten angewendet werden. In den vergangenen 10 Jahren, in denen sich Area Array Bauteile als SMDs erster Wahl durchgesetzt haben, hat sich das Röntgenverfahren für die zerstörungsfreie Inspektion, sowohl bei Inline- als auch Offline-Produktion, etabliert. Die Röntgentechnologie hat sich bei der Aufdeckung typischer Probleme wie Lunker/Voids, Ausrichtungsfehler, Unterbrechungen und Kurzschlüssen bewährt. Darüber hinaus profitiert dieses Verfahren insbesondere von den Entwicklungsfortschritten bei Vergrößerung und Auflösung. Trotzdem schränken die folgenden drei Faktoren den Einsatz dieser Technologie teilweise erheblich ein:

- 1. Korrekte Interpretation der Bilddaten.

- 2. Die Fähigkeit, spezielle Fehler, wie z.B. Delaminierungen in Form von Haarrissen, zu „sehen“.

- 3. Kosten der Systeme.

Die hier behandelte gehäuseseitige Delaminierung von bleifreien Lötverbindungen bei FCs und CSPs stellen selbst die besten 3D-Röntgengeräte vor erhebliche Schwierigkeiten.

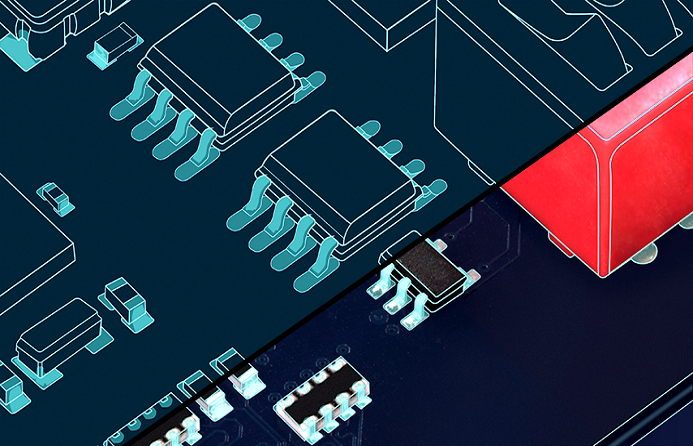

Seit ihrer Markteinführung 1999 haben sich optische BGA-Inspektionssysteme als ideale Ergänzung zu Offline-Röntgenverfahren entwickelt. Bis heute konnte man mit optischen Systemen bei niedrigprofiligen Bauteilen wie Micro BGAs, FCs und CSPs, allerdings nur die leiterplattenseitigen Lötverbindungen inspizieren. In anderen Worten: Die in diesem Artikel erläuterte Problematik der gehäuseseitigen Delaminierung bei FCs und CSPs konnte mit bisherigen optischen BGA-Inspektionssystemen nicht erkannt werden. Die Einführung eines neu entwickelten optischen Inspektionssystems für Flip Chips ermöglicht erst jetzt die visuelle Inspektion der kritischen Defektbereiche und stellt eine kostengünstige Alternative zu zerstörenden Verfahren dar.

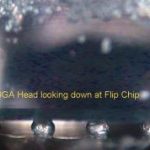

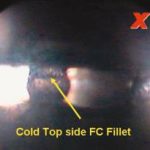

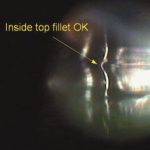

Für die visuelle Inspektion niedrigprofiliger CSPs und FCs sind die erweiterten Möglichkeiten eines neu entwickelten Flip Chip Optikkopfes erforderlich. Die Iris herkömmlicher optischer BGA-Inspektionssysteme befindet sich circa 0,30 mm über der Leiterplattenoberfläche. Dadurch können nur „Draufsichtbilder“ (Bild 13) von Flip Chips erzeugt werden, deren Abstandshöhe in der Regel nur 0,05 mm beträgt. Der neuartige Flip Chip-Inspektionskopf verfügt über eine niedrigere Iris, die sich nur noch circa 0,015 mm über der Leiterplattenoberfläche befindet. Dadurch ist es nun möglich „Ansichten von unten“ zu erzeugen (Bild 14), die auch die Darstellung der gehäuseseitigen Flip Chip-Lötverbindungen zulässt. Es lassen sich also auch mögliche Defekte wie z.B. gehäuseseitige Delaminierungen erkennen. Die kritischen bauteilseitigen Lötverbindungen von FCs und CSPs konnten bisher von keinem optischen BGA-Inspektionssystem auf dem Markt dargestellt werden. Bild 15, 16 und 17 verdeutlichen die Bedeutung dieser Innovation, die beschriebene Problematik gehäuseseitiger Lotkegel-Delaminierung bei einem niedrigprofiligem Micro BGA kann zuverlässig erkannt werden.

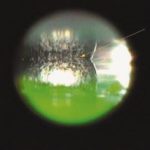

Dank der extrem niedrigen Iris ermöglicht die neue Flip Chip-Optik (Bild 16) sogar die Inspektion gehäuseseitiger Probleme bei innenliegenden Lötverbindungen. Siehe auch Bild 18 und 19, die an dem gleichen Micro BGA (Bild 15) aufgenommen wurden. Das optische Flip Chip-Inspektionssystem wurde bereits erfolgreich zur Erkennung kritischer Defekte bei bleifreier CSP-Produktion eingesetzt. Bei den nachfolgend dargestellten gehäuseseitigen Lötverbindungen eines bleifrei gelöteten CSPs kann man erkennen, dass die mittlere Kugel in Bild 20 einen korrekten Lotkegel aufweist, während die linke Eckkugel in Bild 21 offensichtlich delaminiert ist.

Die Inspektion mittels Röntgen ist Stand der Technik und ein unabdingbares Verfahren zur zerstörungsfreien Inspektion von Leiterplatten. Es sind jedoch gehäuseseitige Delaminierungen mit der Röntgentechnologie nur sehr schwer oder gar nicht erkennbar. Die Aufnahme in Bild 22 wurde mit der neuen Flip Chip-Optik erstellt, Bild 23 mit einem modernen Röntgengerät. Diese Bilder zeigen ganz klar, dass mit einem Röntgensystem alleine eine gehäuseseitige Delaminierung nicht zu erkennen ist. Die Folge: Der 0,02 mm breite Haarriss bei dem oben dargestellten bleifrei gelöteten Micro BGA bleibt unerkannt. Derartige optische Inspektionssysteme zur Ergänzung von Röntgenverfahren sollten deshalb insbesondere bei Bleifreiprozessen als zwingende Notwendigkeit betrachtet werden.

Zusammenfassung

Dieser Artikel behandelt den sehr spezifischen Fehler einer gehäuseseitigen Delaminierung bei Area Array Packages, insbesondere bei FCs und CSPs. Dazu werden aktuelle Fachpublikationen zu dieser Thematik ausgewertet und zusammengefasst. Es wurde gezeigt, dass Bleifrei-Lötprozesse bei diesen Bauteilen neue Prozessbedingungen erfordern. Einfach gesagt wird die Problematik gehäuseseitiger Delaminierung durch den Bleifreiprozess noch verschärft. Als logische Folge müssen adäquate Inspektions- und Testverfahren implementiert werden, um qualitativ hochwertige Bleifrei-Lötprozesse bei FCs und CSPs zu gewährleisten. Werden die oben beschriebenen schwerwiegenden Prozessfehler nicht erkannt, sind Feldausfälle sowie überflüssige Gewährleistungs- und Reparaturkosten unvermeidlich. Leiterplattenproduzenten, die niedrigprofilige Area Array Packages wie z.B. FCs und CSPs in Bleifreiprozessen verarbeiten, sollten den Einsatz moderner optischer Inspektionstechnologien, die zur zerstörungsfreien Erkennung dieser spezifischen Fehler entwickelt wurden, unbedingt in Erwägung ziehen. Die Implementierung lückenloser Nullserien-Inspektionsverfahren, mittels innovativer Inspektionssysteme, stellt eine preiswerte Alternative zur relativ teuren zerstörenden Inspektion dar, bzw. zu den noch höheren Kosten bei unerkannten schwerwiegenden Fehlern. Korrekt informiert und richtig ausgerüstet kann man die Herausforderungen bei der Verarbeitung von FCs und CSPs auch als Chance sehen, die Prozess- und die Produktqualität in einer bleifreien Zukunft zu verbessern.

EPP 421

Quellen:

- 1. „Mechanical Behaviors of Flip-Chip Packaging“ von Professor Toshio Nakamura und Gary Yu Gu

- 2. „3D Interfacial Delamination Near Solder Bumps in Flip-Chip Package“ von Yu Gu und Toshio Nakamura

- 3. „Mechanical Reliability of underfilled CSP Assemblies“ von Murtuza Rampurawala, Michael Meilunas und Arun Gowda & K. Srihari, Ph.D.

- 4. „HDPUG’s Failure Analysis of High-Density Packages’ Lead-Free Solder Joints“ von John Lau, Agilent Technologies; Dongkai Shangguan, Flextronics; Todd Castello, Flextronics; Rob Horsley, Celestica; Joe Smetana, Alcatel; Nick Hoo, Tin Technology; Walter Dauksher, Agilent Technologies; Dave Love, Sun Microsystems; Irv Menis, IBM und Bob Sullivan, HDPUG

- 5. „Reliability of Lead-Free Solder Connections for Area-Array Packages“ von Ahmer Syed, Amkor Technology, Inc.

- 6. „Accumulated Creep Strain and Energy Density Based Thermal Fatigue Life Prediction Models for SnAgCu Solder Joints“ von Ahmer Syed, Amkor Technology, Inc.

Unsere Webinar-Empfehlung

Die Zuhörer erhalten Informationen zur Effizienzsteigerung von AOI-Systemen bei Nutzung von Digitalen Zwillingen von der zu prüfende Baugruppe bzw. des eingesetzten Inspektionssystems.

Teilen: