In der Leiterplattenfertigung erhalten die vom Lötstopplack freigestellten Kupferoberflächen typisch ein „Finish“, um sie einerseits bis zu den Bestückungs- bzw. Lötprozessen zu konservieren, andererseits um definierte dauerhafte Kontaktoberflächen zu schaffen. Es existieren verschiedene Verfahren, die sich sowohl in ihrer technischen Funktion als auch in den anfallenden Prozess- und Materialkosten unterscheiden.

In der Regel erhält die Leiterplatte nur ein einzelnes Finish über die gesamte Oberfläche, welches die Hauptanforderungen erfüllen soll. Um die geforderten Eigenschaften komplett zu erfüllen, werden dabei Teilbereiche der Leiterplatte mit Finish-Eigenschaften versehen, die technisch nicht notwendig sind und daher zu unnötig höheren Kosten führen. Alternativ müssen, um die Kosten geringer zu halten, qualitativ Abstriche gemacht werden.

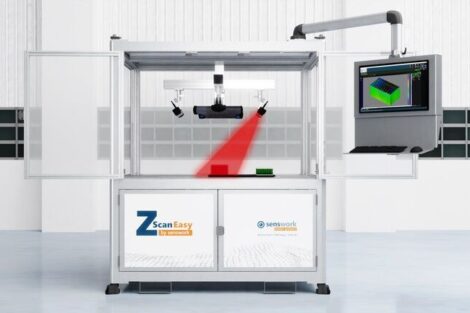

Interessant sind unter diesem Aspekt kombinierte Finish-Oberflächen auf einer Leiterplatte, die auch unter den Begriffen Mixed Metal und Selective Imaging Technologie (SIT) geführt werden. In diesem Beitrag sei hier der selektive ENiG Prozess (SENiG) näher betrachtet.

Der selektive ENiG Prozess wird bevorzugt für die Fertigung von mobilen Endgeräten mit HDI-Technologie eingesetzt. Speziell die Kombination von ENiG mit organischer Surface Protection (OSP) vereinbart die positiven Eigenschaften der beiden Finish-Technologien. ENiG liefert planare Oberflächen mit ausgezeichneten Kontakteigenschaften; sie sind für das Drahtbonden geeignet, abriebfest und lötfähig. OSP hingegen ermöglicht Lötverbindungen mit hohen Festigkeitswerten.

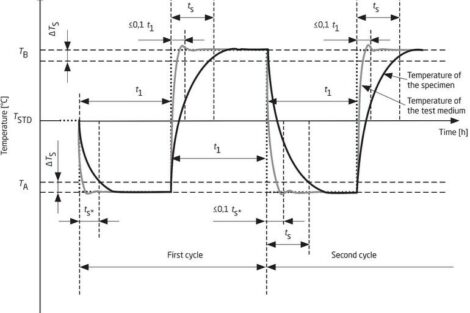

Mobile Endgeräte werden oft mechanisch stärker belastet und entsprechende, mit BGA-bestückte Baugruppen müssen demzufolge vermehrt Stresstests wie Falltests oder Tumble-Tests (in einer rotierenden Trommel) überstehen. ENiG-basierte Lötverbindungen können hier durchaus unzureichende Festigkeiten zeigen. Während OSP hier sehr gute Werte aufweist, ist es im Gegenzug aber für getrennte Kontaktstellen (Tippkontakte, Schaltkontakte, Drehschalter) nicht geeignet.

Ein weiterer nicht unerheblicher Vorteil in diesem Kontext ist die Reduzierung der Goldmenge auf der Leiterplatte und das entsprechende Einsparpotential, wodurch sich der Einsatz der SENiG-Technologie auch für andere Baugruppen mit BGA-Bestückung anbietet.

Für die Leiterplattenproduktion bedeutet dieses selektive Finish-Verfahren einen zusätzlichen Fertigungsprozess, der aber auf typischerweise beim Leiterplattenhersteller vorhandenem Equipment durchgeführt werden kann, und in der gesamtwirtschaftlichen Betrachtung i. d. R. eine positive Bilanz aufweist.

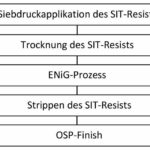

Eine Möglichkeit ist es, die Teilbereiche, die nicht vergoldet werden sollen, zu maskieren. Hier bieten sich Plating Resiste an, die z. B. im klassischen Siebdruck-Verfahren selektiv auf die zu maskierenden Bereiche gedruckt werden. Nach dem ENiG-Prozess können die Resiste dann alkalisch gestrippt werden. Das anschließende OSP-Finish kann üblicherweise ohne weitere Maskierung aufgebracht werden.

Die speziell für diese Technologie entwickelten Plating Resiste zeichnen sich durch eine hervorragende Beständigkeit ohne Leaching im ENiG-Prozess aus und beeinflussen somit die Standzeit und das Metal Turn Over (MTO) der ENiG Bäder nicht negativ. Weiterhin sind ein großes Prozessfenster bezüglich der Trocknung und leichte Strippbarkeit wichtige Parameter, die ein SIT-Resist erfüllen sollte.