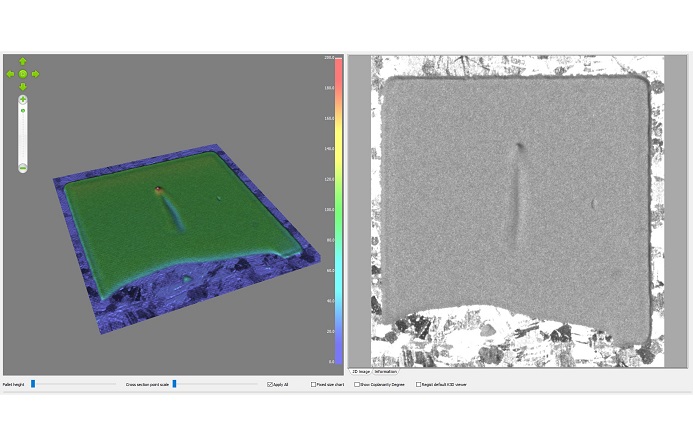

Einen großen Bereich der Bedenken, der mit der Beeinträchtigung des Betriebsverhaltens zusammenhängt, stellt die Tatsache dar, dass die BTCs durchaus eine beträchtliche Abwärme während ihrer normalen Funktion verursachen. Deshalb wird der Wärmeableiter (Thermalpad) des Gehäuses direkt an sein korrespondierendes Gegenstück auf der Leiterplatte zum Abführen dieser Verlustleistung angelötet (Wärmesenke). Leider jedoch können Voids (Fehlstellen), die während des Reflowlötens auftreten, diesen Prozess der Wärmeabfuhr über die Masse der Leiterplatte hemmen oder gar blockieren. Damit besteht das Risiko der Überhitzung für das Bauteil und somit eine potentielle Beeinträchtigung der Zuverlässigkeit des BTC. Eine informelle Befragung von Fertigungsspezialisten zeigte tatsächlich, dass dieses Voiding-Problem heute der größte Bereich von Bedenken in der modernen Elektronikproduktion ist.

Warum bilden sich Voids?

Voids kommen zustande durch die Verflüchtigung des Flussmittels in der Lotpaste beim Lötprozess. Denn Lotpasten besteht zu etwa 50 % ihres Volumens aus Fluxer. Mithin verdampft ein sehr beträchtlicher Teil des ursprünglichen Materials während der Reflowprozedur.

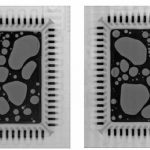

Es gibt keine genormte Festlegung, wieviel Voiding noch akzeptierbar ist. Aber man kann übereinstimmend davon ausgehen, dass insgesamt ein Void-Bereich unter 50 % – und bei großen, zusammenhängenden Voids (Lake, seeförmige Struktur) unter 40 % – als unabdingbare Anforderung dringend einzuhalten sind. Jedoch visiert man, um auf der sicheren Seite zu sein, einen Void-Bereich nicht über 25 % an. In einigen kritischen Anwendungen wie Fahrzeug- oder Sicherheitselektronik sind sogar nur 10 % oder noch weniger verlangt.

Minimieren von Voids: frühere Bemühungen

In der Vergangenheit mussten Prozessingenieure sorgfältig vorbereitete Experimente mit vielen Prozessvariablen vornehmen, um diese zu optimieren, beispielsweise Arbeiten an Reflowprofilen oder Schablonendesign. Mit beträchtlichen Aufwendungen untersuchte man die Effekte aus dem Schablonendesign, damit hier Pfade für ein geordnetes Entweichen des verdampfenden Flussmittels vorhanden sind [1]. Andere Arbeiten befassten sich mit den Vorteilen von Lot-Preforms, mit deren Verwendung der Anteil an massiven Lot in den Wärmesenken (Thermopads) zwischen BTC und Leiterplatte maximiert werden kann [2].

Minimieren von Voids: heutige Arbeiten

mit Reflowofen

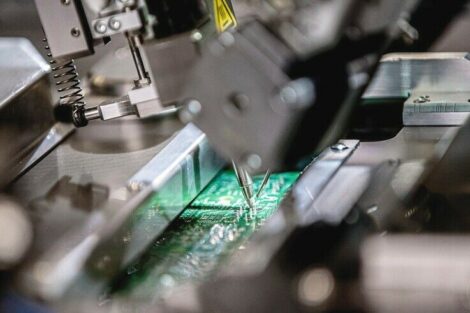

Es erfolgten erhebliche Entwicklungen in der Technik von Reflowöfen, um das Voiding zu minimieren. Äußerst bemerkenswert ist die Anwendung von Vakuum zur Verhinderung von Voids [3]. Berichte zeigen, dass man damit den Anteil der Voids auf nur noch wenige Prozent reduzieren kann. Das ist natürlich eine sehr wichtige Entwicklung, doch muss ein Elektronikunternehmen für die Nutzung dieser Technik entweder einen neuen Ofen kaufen oder zumindest vorhandene Maschinen upgraden. Es gibt zwar einzelne Berichte über vermehrtes Auftreten von Lötzinnspritzern, jedoch könnte mit gezielten Prozessoptimierungen dieses Problem in den Griff zu bekommen sein. Ähnliche Erfolge erzielt man Berichten zufolge mit Reflowöfen, die mit der Anwendung von Ultraschall arbeiten [4]. Ofenhersteller Heller Industries vermerkte in einer Präsentation aus dem Jahr 2016: „Ultraschall wird dann eingesetzt, wenn sich das Lot im flüssigen Zustand befindet.“ Der Ultraschall erzeugt hierbei eine Kavitation, welche die Voids so ausweitet, dass sich diese mit anderen Voids vereinen und sich zum Rand des Lots bewegen oder ausdehnen, wo sie austreten können. Ähnlich wie beim Einsatz von Vakuumöfen müssen die Anwender für die Nutzung dieser Technik entweder in eine neue Maschine oder zumindest in einen Upgrade investieren.

Minimieren von Voids: heutige Arbeiten mit Lotpaste und Prozess

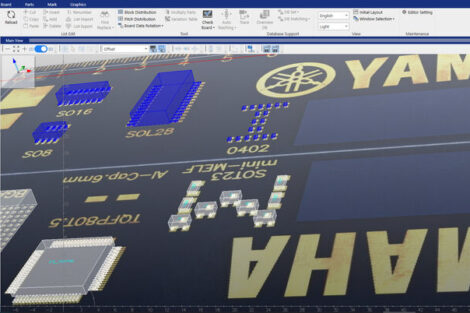

Indium Corporation hat vor kurzem Untersuchungen zur Bestimmung der kritischen Variablen für die Minimierung von Voids durchgeführt. Dies insbesondere mit Blick auf den Einsatz moderner Lotpasten, die gezielt zur Reduzierung von Voiding [5] entwickelt wurden. In Anbetracht der vielen möglichen Variablen wurde ein experimenteller Plan auf der Grundlage folgender Eigenschaften und Daten festgelegt:

- Entekx Plus CU-106A-HT OSP Leiterplattenfinish

- Stahlschablonen mit Dicke 0,004 Zoll (100 µm) und 0,005 Zoll (125 µm), lasergeschnitten, ohne Nano-Beschichtung

- Fensterscheiben-Schablonendesign (Windowpane) im Bereich der Thermopads auf der Leiterplatte, damit flüchtige Anteile entweichen können. Die Rechtecke der Fenster haben ein Kantenmaß von 0,088 Zoll (2,2 mm). Die Druckgeschwindigkeit des Rakels beträgt 100 mm/s, Andruckkraft circa 60 N (6 kg)

- Separationsgeschwindigkeit 5 mm/s bei Entfernung von 2 mm

- Eine Schablonenreinigung (W/D/V) erfolgte vor jeder Bedruckung eines Boards

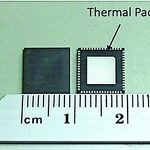

Der verwendete QFN hat eine Rechteckform mit einer Kantenlänge von 7,75 mm (0,3 Zoll).

Der Reflowprozess unter Luft erfolgte einmal mit Profil Nr. 1 – eine direkte Temperaturrampe mit 0,9 °C/s ±0,1 °C/s und einer Spitzentemperatur von 241 °C ±4 °C, hier angewendet für die meisten Untersuchungen. Jedoch wurde auch ein weiteres Profil Nr. 2 für die Bestimmung der Auswirkungen von Reflowprofilen auf Voiding eingesetzt. Eine Anzahl unterschiedlicher Lotpasten kamen zur Anwendung, sowohl mit halogenfreien als auch halogenhaltigen Flussmitteln; außerdem wurden unterschiedliche Lotpulvertypen ausprobiert, so Typ 3, Typ 4, Typ 4.5 und Typ 5.

Dabei wurde etwas sehr vielversprechendes herausgefunden. Profil Nr. 2 (das optimierte Profil für die Void-Reduzierung) minimiert signifikant Voiding von 22 % auf nur noch 8 % im Vergleich zu Profil Nr.1. Hinzu kommt, dass die Standardabweichung der Werte mit Profil Nr. 2 viel enger zusammen lag. Die Schablone mit einer Dicke von 125 µm reduziert Voiding im Vergleich zur 100 µm dicken Schablone um 4,5 %. Das ist wahrscheinlich darauf zurückzuführen, dass die 125-µm-Version einen geringfügig besseren Abstand zum Bauteil bereit stellt, über den die flüchtigen Anteile leichter entweichen können. Beim Vergleich der verschiedenen Lotpulvertypen wurde herausgefunden, dass nur Typ 3 Lotpulver statistisch signifikant auffällige Ergebnisse lieferte, verglichen mit Typ 4, Typ 4.5 und Type 5. Die Paste mit dem Lotpulvertyp 3 führte zu etwa 15 % mehr Voiding.

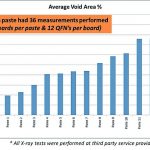

Schließlich wurde abschließend auch noch eine Testreihe durchgeführt, mit der der Einfluss von unterschiedlichen Flussmitteln in den Lotpasten auf dem Umfang von Voiding evaluiert wurde. Jeweils drei Baugruppen, jede mit 12 QFNs bestückt, wurden im Experiment für die Untersuchung jeder Paste verwendet. Die Ergebnisse waren in der Tat verblüffend. Einige Lotpasten führen zu einem Voiding von nur 5 %, hingegen kommen andere auf sehr hohe Werte bis 45 %.

Festgestellt wurde, dass diese Ergebnisse nicht nur verblüffend, sondern auch zusätzlich anspornend wirken. Denn nun sind Lotpasten verfügbar, die entwickelt wurden, um Voiding deutlich zu minimieren.

Referenzen

[1] N.C. Lee et al. http://www.indium.com/technical-documents/whitepaper/voiding-control-for-qfn-assembly [2] Homer, S., Lasky. R.: MinimizingVoiding In QFN Packages UsingSolderPreforms, SMTAI 2011, Fort Worth, TX [3] http://www.circuitnet.com/news/uploads/2/SMT Vacuum void reduction, Sept2012.pdf [4] http://www.hellerindustries.com/Inline-Vacuum-Reflow-System.pdf [5] Diese Arbeit wird detailliert diskutiert in unserem Papier:MinimizingVoiding In SMT Assembly Of BTCs, SMTAI 2016, Chicago, IL