Mit der zunehmenden Komplexität heutiger Systeme stehen Leiterplattendesign-Manager mangels robuster Verifikations-Tools und/oder aufgrund von Schwierigkeiten bei der Anwendung dieser Tools vor der Herausforderung, Probleme frühzeitig in der Design-Entwicklungsphase zu erkennen. Laut einer aktuellen von Lifecycle Insights (Sept. 2018) im Bereich der Elektroniksimulation durchgeführten Designstudie führen 58 % aller Projekte zu zusätzlichen Kosten oder dazu, dass die Markteinführungstermine der Produkte verpasst werden. Gemäß der Studie beträgt die durchschnittliche Anzahl der Design-Respins 2,9 pro Projekt. Dies entspricht 8,5 Tagen ungeplanter Entwicklungszeit bis zur Fertigstellung eines jeden Respins. In der Studie wurde auch festgestellt, dass Leiterplatten-Designteams, die eine „Shift-Left“-Verifikationsmethode in ihren Designprozessen verwendeten, eine 14-prozentige Steigerung bei der termingerechten Projektabwicklung, weniger Respins und eine insgesamt bessere Designqualität erzielten. Laut einer Studie der Aberdeen Group (April 2017) hat für das Management die Time-to-Market zusammen mit der Forderung, Produkte möglichst schnell vor den Wettbewerbern auf den Markt zu bringen, mit die höchste Priorität.

Lösung: Plattform zur Verifizierung von Leiterplattendesigns

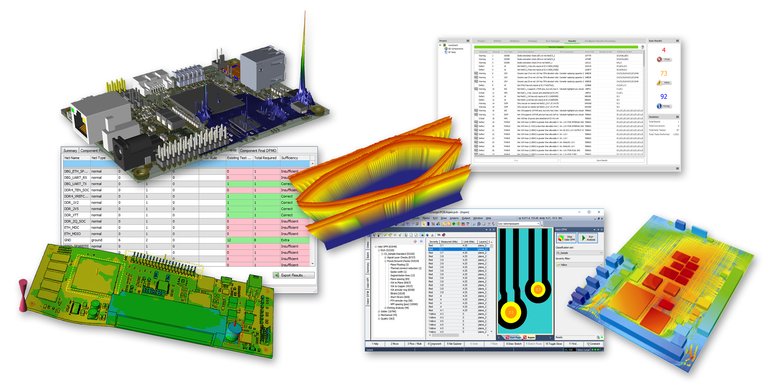

Als der Marktführer im Bereich der Electronic-Design-Automation-Software für Leiterplatten kündigt Mentor, a Siemens business, eine neue mehrdimensionale „Shift-Left“-Verifikationsplattform an. Diese automatisierte Lösung integriert innerhalb einer einzigen Authoring-Umgebung eine breite Palette einfach zu bedienender Verifikations-Tools in eine Leiterplatten-Designplattform, um Probleme frühzeitig im Design, in der Schaltplan- oder Layout-Phase, zu erkennen. Die neue Xpedition-Plattform für Mainstream-Leiterplatteningenieure bietet simultane, „auf Anhieb richtige“ Designanalyse und -verifikation sowie umfassende Tool-Integration. Damit lassen sich erhebliche Zeit- und Kosteneinsparungen bei gleichzeitiger Bereitstellung hochwertiger Produkte erzielen.

Die Verifikationsplattform Xpedition nutzt Best-Practice-Prozesse. Nicht spezialisierte Mainstream-Leiterplattendesigner erlangen damit schnell und intuitiv Simulations- und Analysefunktionen. Integrierte Verifikationstechnologien ermöglichen automatische Modellerstellung, gleichzeitige Simulation, Cross-Probing aus Ergebnissen und Fehlerüberprüfungen in einer einzigen Umgebung. Die neue Xpedition-Plattform ist die umfassendste mehrdimensionale Lösung für die Upfront-Designverifizierung. Sie reicht vom Konzept bis zur Übergabe des Designs und gewährleistet die Herstellbarkeit.

Mehrdimensionale Verifikationslösung

Die Xpedition-Plattform umfasst ein breites Spektrum an robusten Technologien: Schaltplananalyse, Signal-Integritäts- (SI) und Power-Integritäts (PI)-Analyse, Überprüfung der elektrischen Regeln (ERC), thermische Simulation, Schwingungsanalyse, Design-for-Fab (DFF), -Assembly (DFA) und -Test (DFT) sowie Prüfung der Herstellbarkeit. Diese integrierten Technologien, die in einer einzigen Authoring-Umgebung zum Einsatz kommen, die dem Designer oder Designteam vertraut ist, ermöglichen die frühe Erstellung von virtuellen Designprototypen. Die neue Verifikationsplattform Xpedition umfasst führende Technologien in mehreren Bereichen:

Verifizierung des Schaltplanentwurfs: Einzigartiges, vollautomatisches und leistungsstarkes Tool zur Integritätsprüfung von Schaltplänen. Das Tool ersetzt die manuelle visuelle Schaltplanprüfung und reduziert Respins in einem frühen Designstadium um bis zu 70 Prozent.

Design-for-Test-Analyse: Identifiziert die Testpunktanforderungen. Diese werden als Bedingungen automatisch vom Schaltplan an das Layout übergeben und verbessern dadurch die Testbarkeit. Die Funktion erzeugt Test- und Inspektionsdaten für Maschinen in der Prozessvorbereitung mit frühzeitiger Diagnose und senkt so die Gesamtkosten der Prüfung.

Design-for-Manufacturability- (DFM) Analyse: Diese führende Technologie bietet eine umfassende DFM-Analyse, die Fertigung, Montage, Test, Flex/Starrflex, Substrat- und Panel-Validierung frühzeitig und zeitgleich während des Leiterplattendesigns umfasst, ohne das Layout in der neuen Xpedition-Integrationsumgebung zu verlassen.

Sign-off der elektrischen Leistung: Durch die automatische Überprüfung der elektrischen Regeln (ERC) simultan zum Leiterplatten-Layout lassen sich kritische Signal-Integrität, Power-Integrität und EMI/EMC-Probleme schnell identifizieren und die Designüberprüfung von Tagen auf wenige Minuten zu beschleunigen.