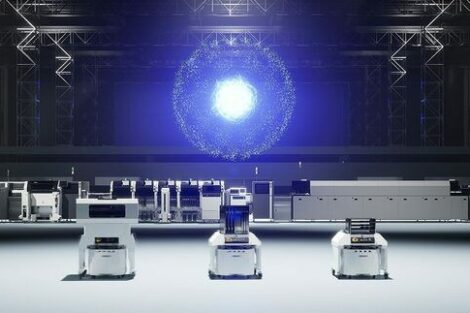

Der Trend zur Miniaturisierung der Leistungsbauteile ist nicht aufzuhalten. Immer wichtiger wird dabei die verlustfreie Wärmeleitfähigkeit der Lötstellen im SMT-Prozess, um zuverlässig reproduzierbare Lötergebnisse in höchster Qualität zu erzielen. Während des Lötprozesses können Voids entstehen, die den effektiven Wärmeübergang schwächen und zur thermischen Schädigung der Leistungsbauteile führen – bis hin zum Ausfall. Um dem entgegenzuwirken, hat Ersa mit Voidless ein neues Verfahren entwickelt, das die Voidbildung während des Lötprozesses auf ein absolutes Minimum reduziert. Zum Einsatz kommt das Voidless-Modul in einer Ersa Reflowlötanlage vom Typ Hotflow 3/20 als Ergänzung bestehender Peakzonen, womit auch das Erreichen des schmelzflüssigen Zustandes einer Lotverbindung bei massereichen Bauteilen gewährleistet ist.

Wie kam es zu Voidless? Schon 2012 beschäftigte sich das Unternehmen mit alternativen Verfahren zur Voidminimierung. Gemeinsam mit dem Fraunhofer Institut für Silicatforschung (ISC), das über langjährige Kompetenz und Erfahrung auf dem Gebiet Adaptronik verfügt, wurde eine Machbarkeitsstudie durchgeführt, um theoretische Vorüberlegungen seitens Ersa in der Praxis zu bestätigen. Die Entwicklung umfasst ein Universalverfahren zur Voidminimierung im flüssigen Lot zwischen Leiterplatte und Bauteil mittels einer mechanischen, sinusartigen Sweep-Anregung des Leiterplattensubstrats, wobei primär eine Longitudinalwelle mit einer Amplitude von wenigen µm in der Leiterplattenebene angeregt wird –unabhängig von der verwendeten LP-Geometrie. Die niedrigen Anfangsfrequenzen des Sweeps bewirken eine schonende und homogene Schwingungsausbreitung in der Leiterplatte, ohne Molekülketten (z.B. FR4) zu schädigen. Bei höheren Frequenzen führt die Frequenzsteigerung zu einer Versteifung des Leiterplattensubstrats, einer Erhöhung des E-Moduls und infolge eines geringeren Dämpfungsfaktors zur besseren Energieübertragung auf das flüssige Lot. Bereiche mit niedrigerer Dichte – die „Voids“ – werden dabei aus dem flüssigen Lot „hinausvibriert“. Das flüssige Lot auf der Leiterplatte wird somit mehrfach durch die Schwingungsausbreitung in der Leiterplatte in eine Relativscherbewegung angeregt, was zur Voidminimierung der Lötstellen führt. Zahlreiche Untersuchungen am Fraunhofer ISC haben die hohe Dämpfungswirkung des Lotes nachgewiesen.

Zusammenfassend lässt sich festhalten: Die Hotflow 3/20-Voidless verbindet die bewährte Reflowlöttechnologie des Unternehmens mit der innovativen und patentierten Voidless-Option, die bei Bedarf einfach zu- oder abschaltbar ist und den Kunden höchste Flexibilität im Produktionsprozess bietet. Bereits wenige Sekunden genügen, um die Voidrate um bis zu 98 % gegenüber einem herkömmlichen Lötprozess zu reduzieren. Weitere positive Nebeneffekte sind zudem eine Zentrierung der Bauteile auf dem Lotpad und eine optimierte Benetzung des Lotes auf dem Pad darunter. Delaminationen des Leiterplattensubstrates oder Popcorn-Effekte der Bauteilgehäuse treten dabei mit dieser Option nicht auf. Zusätzliche Bauteilspezifizierungen sowie MSL-Level (Trocknung der Komponenten) wie bei Alternativprozessen sind nicht erforderlich. Die Hotflow 3/20-Voidless überzeugt mit kurzen Taktzeiten, nahezu wartungsfreiem Betrieb, einer idealen Energiebilanz und optimierter Prozesskontrolle bei höchster Maschinenverfügbarkeit – und vor allem: mit einer Restvoidrate von bis unter 2 %!

Unsere Webinar-Empfehlung

Im Webinar werden Funktionen von AOI-Systemen und der angrenzenden Peripherie aufgezeigt, welche das Risiko von Fehlern bei der AOI-Programmerstellung, der Inspektion sowie der anschließenden manuellen Verifikation nahezu ausschließen. Ziel ist es dabei, Fehlerschlupf zu vermeiden…

Teilen: