Durch Chip-Size Packaging über den ganzen Wafer hinweg ist es den Wissenschaftlern am Fraunhofer-Institut für Siliziumtechnologie ISIT in Itzehoe gelungen, die Kosten für die Verpackung von Siliziumschaltungen mit mittleren Anschlusszahlen sowie von integrierten passiven Hochfrequenzbauteilen erheblich zu reduzieren. Die kleinen, robusten Bauteile zeichnen sich durch eng tolerierte Lotkugeln mit genau definierter Lotzusammensetzung aus.

Jessica Pontow & Wolfgang Reinert, Fraunhofer-Institut für Siliziumtechnologie ISIT, Itzehoe

Da portable Kommunikations- und Medizingeräte immer kleiner werden, muss die Vielzahl elektronischer Bauelemente möglichst Platz und Gewicht sparend auf einer Leiterplatte bestückt werden. Ein wesentlicher Schritt zur Erhöhung der Packungsdichte ist die Chip-Size-Packaging-Technologie (CSP), wobei die Anschlusskontakte – meist in Form von Lotkugeln – gleichmäßig über die gesamte Chipfläche verteilt sein können. Die Größe des gefertigten Bauelements entspricht dann der Grundfläche des Siliziumchips. Jedoch ist der konventionelle Herstellungsprozess von einzelnen Chip-Size Packages mit Umverdrahtungssubstrat technisch und personell aufwändig und damit relativ teuer.

Lösen lässt sich dieses Problem nur durch gleichzeitiges Packaging aller auf einem Wafer befindlichen Bauelemente (Wafer Level Packaging). Der Prozess, der die Umverdrahtung, das Aufbringen einer Schutzpassivierungsschicht, die Anschlusskontaktierung sowie den Test und anschließend die Vereinzelung der Chips beinhaltet, birgt aber auch völlig neue Herausforderungen. So müssen beispielsweise auf Wafer Level 50.000 bis 100.000 Lotkugeln gleichzeitig und exakt auf den Chip Pads platziert werden. Die Experten des Fraunhofer-Instituts für Siliziumtechnologie ISIT haben sich intensiv mit diesem Thema auseinander gesetzt. Mit Erfolg: In Itzehoe steht seit Ende 2003 Europas einzige für die industrielle Fertigung voll qualifizierte Wafer-Level-Packaging-Linie.

Balling auf Wafer Level

Ein grundlegender Fertigungsschritt der Chip-Size-Packaging-Technologie ist das Aufbringen der Kontakte in Form von Lotkugeln, das Balling. Ausgangsmaterial ist in der Regel ein 0,4 mm dünner Siliziumwafer mit prozessierten Chips, die meist für das Draht-Bonden ausgelegt sind. Um die sich an der Chip-Peripherie befindlichen Kontakte über die gesamte Chipoberfläche zu verteilen, kann auf der Under-Bump-Metallisierungsebene die Kontaktierung umverdrahtet werden. Die aus Aluminium oder einer Al-Legierung bestehenden Bond Pads weisen eine Fläche von 100 x 100 µm auf und sind 1 µm stark. Sie sind bis zum Rand hin etwas überlappend mit einer 1 µm dünnen Siliziumnitrid- oder Siliziumoxidnitridschicht stresskompensiert überdeckt. Um auf die Pad-Mitte die Lotkugeln auflöten zu können, muss zuerst ein anderes lötfähiges Material aufgebracht werden, weil sich Aluminium wegen seiner Oxidhaut nicht löten lässt.

Thermisch stabile Under-Bump-Metallisierung

Für die Under-Bump-Metallisierung (UBM) verwenden die ISIT-Wissenschaftler einen Drei-Schicht-Verbund, bestehend aus einer Aluminiumschicht, mit der das Al Bond Pad kontaktiert wird, einer Diffusionsbarriere aus Nickel-Vanadium und einem darüber liegenden Kupfer-Layer. Damit lässt sich eine thermisch stabile Schichtstruktur erzeugen, die an der Oberfläche lötbar ist und an der Unterseite einen guten Kontaktwiderstand aufweist. Die Zwischenschicht aus Nickel-Vanadium dient ausschließlich dazu, die Lebensdauer und Qualität bei hohen Temperaturen der Schaltungen sicherzustellen.

In einem nachfolgenden Schritt wird der komplette Wafer mit einem 5 µm dünnen BCB-Layer (Benzo Cyclo Buten) passiviert, wobei die Pads auszusparen sind. Diese recht teure BCB-Schicht kann durch Verwendung des speziellen, am ISIT entwickelten Nassätz-Prozesses allerdings auch weggelassen werden.

Aufdrucken des Flussmittels

Auf das Löt-Pad wird nun durch eine Schablone ein kleines Flussmitteldepot aufgedruckt, das die Aufgabe hat, eine der vorgeformten Lotkugeln zu halten, etwas anzunetzen, zu zentrieren und beim nachfolgenden Reflow-Prozess zu löten. Die Reste des Flussmittels lassen sich anschließend mit Wasser abwaschen. Es ist wichtig, ein Flussmittel zu verwenden, das ausreichend druckbar, klebrig, genügend aktiviert und abwaschbar ist und sich darüber hinaus für die Prozesstemperatur von zirka 250°C eignet.

Beim Aufrakeln der genau definierten Menge an Flussmittel kommt es auf eine sehr genaue Mitte-zu-Mitte-Positionierung an, da ansonsten die Kugel vom Pad heruntergezogen wird. Bei den heutigen Lotkugeln mit 300 µm Durchmesser beträgt der Abstand zwischen den einzelnen Kugeln in der Serienfertigung 500 µm. Das Ziel ist ein Pitch von 200 µm mit 80 bis 100 µm kleinen Lotkugeln. Das bedeutet, dass auf einer Chipfläche von 5 x 5 mm etwa 100 Kugeln Platz fänden. Bei 200 µm Pitch wären dies dann etwa 580 Kugeln pro Bauelement.

Aufbringen der Lotkugeln

Auf die mit Flussmittel bestrichenen Pads lassen sich jetzt die Lotkugeln aufbringen. Dazu wird der Wafer von unten angesaugt und fixiert. Die darüber fein justierte Schablone liegt mit einem gewissen Absprung (Neigungswinkel) über der Siliziumscheibe, damit nach dem Einschütten der Kugeln die überschüssigen Teile ablaufen können. Je eine Lotkugel fällt jeweils in ein Loch der Schablone und klebt am Flussmittel fest. Die Kugeln bestehen aus einer speziellen Legierung und sind standardmäßig von einem deutschen Hersteller lieferbar. Der mit Lotkugeln bestückte Wafer geht dann direkt in den Reflow-Lötofen. Nach einer Reinigung des Wafers werden alle Lotkugeln auf Fehler inspiziert und ein elektronischer Wafer Map erstellt.

Testen und Burn-in

Die Chips können anschließend, also noch vor dem Sägen, gleichzeitig getestet werden und bei Bedarf einen Burn-in-Prozess durchlaufen (Wafer Level Reliability). Die Möglichkeit, alle Bauteile während des Burn-in-Prozesses zu testen, führt zu einer massiven Reduzierung der Testzeiten. Dieses Verfahren ist technisch allerdings sehr anspruchsvoll, da mehr als 20 000 Pads direkt auf der Siliziumscheibe simultan mit hoher Zuverlässigkeit und bei Temperaturen von 120 bis 150 °C kontaktiert werden müssen.

Sensoren auf aktivem Chip

Die CSP-Technologie auf Wafer Level bietet sich in erster Linie für die Herstellung von kleinen, robusten Siliziumschaltungen mit niedrigen bis mittleren Anschlusszahlen und für integrierte passive Hochfrequenzbauteile an. Die meisten der heute im ISIT gefertigten Bauelemente wandern in Applikationen, in denen es auf hohe Integrationsdichte ankommt, also beispielsweise in mobilen Kommunikations- und Consumergeräten (MP3-Player, digitale Diktiergeräte) oder auch in Hörgeräten und Uhren. CSPs sind jedoch nicht auf rein mikroelektronische Schaltungen beschränkt, zukünftige Entwicklungen zielen in Richtung Kombination von Mikrosystemtechnik mit der CMOS-Technologie. So lässt sich beispielsweise für die Anwendung in Hörgeräten ein Miniatur-Mikrofon auf einen aktiven Chip löten. Im Rahmen des neuen EG-Projekts DAVID soll außerdem ein CSP-MEMS zur Bewegungsmessung realisiert werden, wobei auf jeden 3 x 3 mm kleinen Chip vier Sensoren aufgelötet werden.

Wafer Level Packaging am ISIT

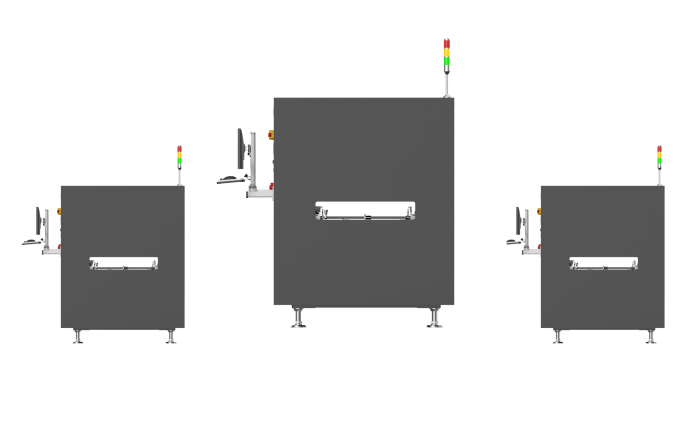

Seit nunmehr zwei Jahren werden in Itzehoe im industriellen Maßstab Chips aufgebaut. Inzwischen ist der Prozess für 6 Zoll Wafer Level Packaging nach ISO 9001 und ab 2006 auch nach TS16949 für Automotive-Anwendungen qualifiziert. Zug um Zug wird die Fertigung nun auf 200-mm-Siliziumscheiben umgestellt. Die Produktionslinie ist für kleine bis mittlere Wafer-Stückzahlen ausgelegt mit hoher Flexibilität auf verschiedene Kundenanforderungen. Auch der RoHS-Diskussion wird dabei selbstverständlich Rechnung getragen. Beim überwiegenden Teil der laufenden Projekte kommen bereits bleifreie Lotkugeln zum Einsatz.

EPP 463

Packaging Service am ISIT

Speziell für kleinere und mittlere Stückzahlen bietet das Fraunhofer-Institut für Siliziumtechnologie ISIT die innovative CSP-Technologie auf Wafer Level als Dienstleistung an. Im Fokus stehen mittelständische Unternehmen und im Umgang mit dieser Technologie noch nicht so vertraute Kunden mit wenigen für die Technologieerprobung und Zuverlässigkeitsbewertung zu prozessierenden Wafern. Auch für das Prototyping bietet sich der Service an. Die Vorteile für den Kunden liegen klar auf der Hand: Zum einen haben auch Aufträge dieser Größenordnung im ISIT eine hohe Priorität, zum anderen sind die Wege zum Kunden kurz, so dass auftretende Designänderungen schnell in die Fertigung einfließen können.

Unsere Webinar-Empfehlung

10.10.22 | 10:00 Uhr | Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine…

Teilen: