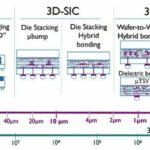

Bis vor kurzem war die Großserienfertigung des Wafer-to-Wafer-Hybridbondens hauptsächlich auf den Bereich Stacked Imagesensoren auf signalverarbeitenden Schaltungen beschränkt. In jüngerer Zeit wird die Technik auch für die Integration von CMOS-Peripherieschaltungen auf 3D-NAND-Schichten eingesetzt. Diese Anwendungen profitieren von der Möglichkeit der Technologie, eine Million Verbindungen pro mm2 zu integrieren, was durch einen engen Cu-Verbindungsabstand von etwa 1 µm ermöglicht wird. Ein weiterer Vorteil ist die Möglichkeit, verschiedene Materialien und Funktionalitäten sowie CMOS-Technologien unterschiedlicher Generationen zu kombinieren.

Mit Hilfe der Systemtechnologie-Co-Optimierung (STCO) wird die Partitionierung von Schaltkreisen auf immer niedrigeren Ebenen der Designhierarchie erfolgen. Um das Potenzial des Wafer-to-Wafer-Hybrid-Bonding dabei voll auszuschöpfen, muss es den Forschern gelingen, den Pitch der Verbindungen weit unter 1 µm zu skalieren.

Prozessablauf für das Wafer-to-Wafer Hybrid-Bonden

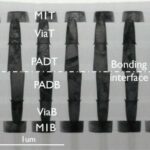

Die heutigen Prozessabläufe für das Hybrid-Bonden von Wafer zu Wafer beginnen mit zwei vollständig prozessierten 300-mm-Wafern mit abgeschlossenem Front-End-of-Line (FEOL) und Back-End-of-Line (BEOL). Der erste Teil des Prozesses ähnelt einem On-Chip BEOL Damascene-Prozess, bei dem kleine Kavitäten in das Bonding-Dielektrikum geätzt werden – wofür überwiegend SiO2 verwendet wird. Die Hohlräume werden mit Barrieremetall, Seed und Cu gefüllt. Danach folgt ein chemisch-mechanischer Polierschritt (CMP), der für eine hohe Gleichmäßigkeit über die Wafer hinweg optimiert ist, um extrem plane dielektrische Oberflächen zu erzeugen und gleichzeitig eine Vertiefung von wenigen Nanometern für die Cu-Pads zu erzielen. Nach der präzisen Ausrichtung wird das eigentliche Bonden der beiden Wafer bei Raumtemperatur durchgeführt, indem die Wafer in der Mitte des Wafers in Kontakt gebracht werden. Die polierte Oberfläche der Wafer führt zu einer starken Anziehungskraft zwischen den Wafern, was zu einer Bondwelle führt, die den Spalt zwischen den Wafern von der Mitte zum Rand hin schließt. Nach diesem Schritt des Bondens bei Raumtemperatur werden die Wafer bei höheren Temperaturen getempert, um eine dauerhafte dielektrische und Cu-zu-Cu-Bindung zu erzielen.

Neue Anwendungen, neue Prozessschritte?

Mit der Ausweitung des Anwendungsbereichs entstehen immer fortschrittlichere Implementierungen des Hybrid-Bonding. Wie bereits erläutert, geht der Trend dahin, den Bondprozess immer näher an das Frontend zu verlagern, um beispielsweise Logik-auf-Logik oder Speicher-auf-Logik-Stacking zu ermöglichen. Dies erfordert auch eine stärkere Nachbearbeitung nach dem Bondprozess.

Ein spezifisches Beispiel ist ein Backside Power Delivery Network (BSPDN), für das das Wafer-to-Wafer-Bonden ein entscheidender Schritt ist. Bei der BSPDN-Verarbeitung wird die Vorderseite des ersten Wafers auf einen Trägerwafer geklebt. Die Rückseite des ersten Wafers wird dann gedünnt und der Prozess wird durch n-TSV-Strukturierung, Metallfüllung und Rückseitenmetallisierung abgeschlossen. In diesem Beispiel wird ein Teil der BEOL-Verarbeitung nach dem Wafer-Bonding-Prozess durchgeführt. Die Anwendungen stellen strengere Anforderungen an die Skalierung, die eine Herausforderung für den aktuellen Prozessablauf darstellen. Die Hauptprobleme betreffen die Genauigkeit der Cu-zu-Cu-Ausrichtung, die Reinheit des Wafers und die Topologie vor dem Bonden sowie die Bindungsstärke der Dielektrika und der Cu-Pads bei kleinen Pitches für die Verbindungen.

Hybride Wafer-to-Wafer-Bonding-Prozesse

Designverbesserungen zur Kompensation von Limitationen bei Skalierung und Ausrichtung:

Imec-Forscher haben zum ersten Mal ein Versuchsträgerdesign mit einem sechseckigen Gitter und kreisförmigen Cu-Pads anstelle des traditionellen quadratischen Gitters mit einem quadratischen oder kreisförmigen Pad-Design vorgeschlagen. Das neue Design bietet mehrere Vorteile. Es ermöglicht eine besonders dichte Packung der Cu-Pads mit gleichen Abständen zwischen allen benachbarten Pads. Bei weiterer Skalierung erleichtert eine solche Konfiguration die Kontrolle der Cu-Pad-Dichte bei gleichzeitiger Maximierung der Cu-Padgröße und der Abstände. Das Team untersucht auch, welche Auswirkungen die Verwendung eines gleichen oder ungleichen Pad-Designs hat. Im letzteren Fall wird der obere Wafer mit kleineren kritischen Cu-Pad-Abmessungen entworfen als der untere Wafer. Ungleiche Pad-Designs bieten einige Vorteile, darunter eine größere Toleranz beim Bonding-Overlay, eine geringere parasitäre Kapazität und eine höhere dielektrische Durchschlagsfestigkeit bei kleinen Interconnect-Abständen.

Genaue Kontrolle der Oberflächentopografie:

Bevor die beiden Wafer miteinander gebondet werden, müssen die Oberflächen beider Wafer extrem plan und sauber sein, um einen zuverlässigen Hybridbondprozess zu erreichen. CMP ist daher ein sehr anspruchsvoller Prozessschritt. Darüber hinaus ermöglicht CMP eine einheitliche Vertiefung der Cu-Pads, was bedeutet, dass das Cu vor dem Bonden einige Nanometer unterhalb der dielektrischen Oberfläche bleibt. Dies ist erforderlich, um nach dem Tempern eine lunkerfreie Verbindung zu erhalten. Durch die Kombination eines fortschrittlichen CMP-Prozesses mit Dummy-Pads im Layout-Design gelang es den Forschern, die Höhe der Cu-Pads und die Oberflächentopologie auf dem gesamten Wafer genau zu kontrollieren.

SiCN-Dielektrikum für erhöhte Bindungsstärke und Skalierbarkeit:

Imec hat bereits früher SiCN als Dielektrikum der Wahl für kleine Leiterbahnabstände vorgeschlagen. SiCN-Oberflächen weisen im Vergleich zu SiO2-Oberflächen eine höhere Bindungsenergie auf, d. h. es ist mehr Energie erforderlich, um die Bindung zu brechen. Außerdem fungiert SiCN als Diffusionsbarriere für Cu und eine Wafer-Passivierungsschicht, die die Gasdiffusion blockiert, was zu einer thermisch stabileren Bindungsschnittstelle führt. Diese Eigenschaften sind von zunehmender Bedeutung bei der Skalierung der Hybridbond-Verbindungsabstände. Messungen auf der Grundlage der Nanoindentation – einer immer häufiger angewandten Technik zur Bewertung der Bindungsstärke – bestätigten, dass die SiCN-SiCN-Bindungsstärke die von SiO2-SiO2 deutlich übertrifft. Die hohe Bindungsstärke kann nach dem Tempern bei nur 250°C erreicht werden und verschlechtert sich auch bei höheren Temperaturen nicht.

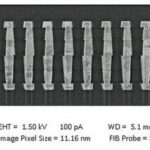

400 nm Pitch Interconnects mit sehr guter elektrischer Leistung

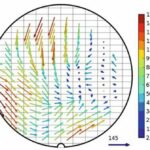

Die oben genannten Erkenntnisse wurden genutzt, um einen fortschrittlichen Wafer-zu-Wafer Cu/SiCN-Bonding-Prozess durchzuführen. Das eigentliche Bonden wurde mit einem handelsüblichen hochwertigen Wafer Bonder durchgeführt, der mit fortschrittlichen Ausrichtungsfunktionen ausgestattet ist – ein Werkzeug, das für den Erfolg des Prozesses entscheidend ist. 300-mm-Wafer wurden erfolgreich gebondet, wobei Cu-Verbindungen mit einem noch nie dagewesenen Pitch von nur 400 nm hergestellt wurden. Die Ergebnisse zeigen eine erfolgreiche Kontrolle der Cu/SiCN-Oberflächentopographie, eine präzise Ausrichtung (die zu einer Überlappung von weniger als 150 nm führt) und eine günstige elektrische Leistung (d. h. einen niedrigen Einzelkontaktwiderstand).

Notwendige Überlappung

Zum ersten Mal untersuchte das Team auch die Beziehung zwischen dem Bonding-Overlay und der Zuverlässigkeit (d. h. dielektrischer Durchschlag und Ausbeute). Die Ergebnisse bestätigen, dass die dielektrische Durchschlagsfestigkeit von ungleich gestalteten Cu-Pads höher ist als die von gleich gestalteten Pads bei kleinen Interconnect-Abständen. Das Team kam außerdem zu dem Schluss, dass bei diesen 400 nm großen Leiterbahnabständen die Überlappung kleiner als 100 nm sein muss, um eine ausreichende Ausbeute in der Massenfertigung zu erzielen. Daher stellt die Erfüllung der Anforderungen zukünftiger 3D-SOC-Designs hohe Anforderungen an die Overlay-Genauigkeit von Wafer-Bonding-Anlagen der nächsten Generation.

Fazit

Das Wafer-to-Wafer-Hybrid-Bonding hat sich als vielversprechende 3D-Integrationstechnologie erwiesen, die eine zunehmende E/A-Dichte und effizientere Verbindungen zwischen funktionalen Dies ermöglicht. Um Anwendungen wie Memory-on-Logic zu ermöglichen – bei denen das Wafer-to-Wafer-Bonding nahe am Front-End stattfindet – muss die Skalierung der Cu-Verbindungssteigung bis an ihre Grenzen getrieben werden. Verbesserungen im Grid-Design, eine verbesserte Kontrolle der Oberflächentopographie, die Verwendung von SiCN als Dielektrikum, ein grundlegendes Verständnis der Bondmechanismen und eine verbesserte Überlappungskontrolle sind die wichtigsten Voraussetzungen für die Realisierung von elektrisch funktionalen und zuverlässigen Cu-Verbindungen mit einem Pitch von 400 nm (und kleiner). Diese Ergebnisse bilden die Grundlage für die Entwicklung zukünftiger Wafer-to-Wafer-Bonding-Prozesse mit noch geringeren Abständen zwischen den Verbindungen.

Literaturnachweis

[1] ‘The challenges of Cu/SiCN wafer-to-wafer hybrid bonding scaling down to 400nm pitch,’ S.A. Chew et al., IEDM 2023;

[2] ‘New Cu “bulge-out” mechanism supporting sub-micron scaling of hybrid wafer-to-wafer bonding,’ J. De Messemaeker et al., 2023 IEEE Electronics Components and Technology Conference (ECTC).