Die Entwicklung elektronischer Baugruppen ist seit ihrer frühesten Phase von produktions- und zulieferbedingten Fehlern begleitet. An diesem Zustand hat sich trotz enormer Entwicklungs- und Produktionsverbesserungen nichts geändert. Denn trotz fehlerfreier Beherrschung einer Technologie werden neue und vor allem schwierigere Herausforderungen angenommen.

Neue Herausforderungen bedeuten im Falle elektronischer Komponenten sich ständig erweiternde Komplexität. Und die zunehmende Komplexität der Bauteile ist natürlich Nährboden für auftretende Fehler. Da fehlerhafte Baugruppen nicht ausgeliefert werden dürfen, ist eines logischerweise klar: Es muss getestet werden!

Nun gibt es verschiedene Test-Technologien, die je nach Bedarf und Aufwand eingesetzt werden. Ob es sich um den In-Circuit-Test (ICT), den Flying Probe Test (FPT), den Funktionstest (FT), die Automatische Optische Inspektion (AOI) oder den Boundary Scan Test handelt, alle Techniken haben ihre Vor- und Nachteile. Jedoch wird in heutiger Zeit ein Faktor immer entscheidender: die Kosten. Welche Kosten durch welchen Test verursacht werden, hängt von den Anschaffungskosten des Testsystems und entscheidend vom Aufwand im Prozess ab. Dabei fallen auf letzteres die Kosten für:

- Testvorbereitung

- Testdurchführung

- Fehlersuche.

Doch nicht nur die Kosten, sondern auch weitere Spezifika sind wichtig für die Auswahl der Testtechnologie, denn jede Testart bringt diverse Probleme mit sich.

Vor- und Nachteile verschiedener Testverfahren

Die Nachteile der bereits o.a. Testverfahren sind im Folgenden aufgeführt:

Funktionstest:

- sehr hohe Kosten bei der Prüfprogrammerstellung (Aufwand mehrere Wochen bis Monate)

- sehr hohe Kosten bei der Fehlersuche

- Test aller Funktionen und dadurch Abdeckung aller möglichen Fehler praktisch nicht möglich.

In-Circuit-Test:

- hohe Kosten bereits in der Testvorbereitung durch prüflingsspezifischen Adapterbau

- Extrakosten bei Layoutänderungen

- hohe Kosten der Lagerung und Instandhaltung der Adapter

- Nadelplatzierung wird durch Erhöhung der Leiterzugdichte immer schwieriger

- bei hochpoligen BGAs ist eine Adaptierung über Nadeln nicht möglich; Kontaktierung von Pads ist nicht sinnvoll, da der Vorteil der Höchstintegration (Platzersparnis) durch diese zunichte gemacht würde (Bild 2).

Automatische Optische Inspektion:

Fehlererkennung an verdeckten Lötstellen nicht möglich.

Flying Probe Test:

- hohe Prüfzeiten aufgrund der sequenziellen Antastung der Prüfpunkte

- Wartungskosten für verschleißende Kontaktspitzen und bewegte mechanische Teile.

Testfreundlicher Entwurf von digitalen Schaltungen

Um diesen Nachteilen der genannten Testverfahren in der Fertigungsprüfung zu begegnen, ist es notwendig, die Nutzung schaltungseigener Möglichkeiten für die Prüfung zu forcieren. Grundvoraussetzung hierfür: die Entwicklung eines Prüfkonzepts mit allen notwendigen Hard- und Softwareelementen in der zu prüfenden Baugruppe. Diese Anstrengungen werden als „Prüfgerechte Gestaltung“ oder auch „Design for Testability (DFT)“ bezeichnet.

Wenn man die zu testenden Objekte betrachtet, stellt man fest, dass der Anteil digitaler Schaltungen in den letzten Jahren enorm zugenommen hat. Dies lässt sich am Beispiel moderner Unterhaltungselektronik aufzeigen, da gerade hier der Trend weg von analoger hin zu digitaler Technik geht, stark indiziert bei Radios oder Fernsehgeräten. Diesen Trend gilt es bei der Auswahl der Teststrategie zu nutzen, wobei die Probleme des Testens der digitalen Schaltung eine ernst zu nehmende Rolle spielen.

Man geht von zwei Schwerpunktproblemen bei der Prüfung digitaler Schaltungen aus: Testsatzgenerierung und Testverifizierung.

Die Testsatzgenerierung wird als Prozess zur Gewinnung von Stimuli-Signalen für eine Schaltung bezeichnet, um deren korrekte Funktion nachzuweisen. Die Testverifizierung soll das Antwortverhalten der Schaltung ermitteln. Gleichzeitig wurden die automatische Testsatzgenerierung und Testverifizierung mit steigender Komplexität der Baugruppen immer schwieriger. Dies lässt sich am besten am Beispiel eines Funktionstests verdeutlichen. Dazu wird unterstellt, dass jede digitale Schaltung in sequenzielle und kombinatorische Schaltungsteile zerlegbar ist (Bild 3).

Nach Moore und McCluskey errechnet sich die Mindestzahl an Testvektoren für einen 100%igen Funktionstest wie folgt:

Q = 2(x+y)

x = Zahl der Eingänge

y = Zahl der Speicherelemente (sequenzielle Schaltungsteile).

Bei einer angenommenen Schaltung, die aus 25 Eingängen (x) und 50 internen Latches (y) besteht, erfordert eine Testrate von 100 ns pro Testschritt eine Testzeit von 107 Jahren.

Dieses Testproblem kann überwunden werden, indem man Schaltungen entwirft, die einfacher testbar sind, und bei denen die sequenziellen Schaltungsteile genutzt werden. Man designed sozusagen, um problemlos mit geringer Fehlerabdeckung und in akzeptabler Zeit testen zu können, und zusätzlich das Problem des Testzugriffs zu überwinden. Diese prüffreundlichen Entwürfe nennt man Design for Testability.

Unterteilung des DFT

Ad-Hoc-Design

Es beinhaltet die Partitionierung, die Einführung zusätzlicher Testpunkte und die Anwendung von Bus-Architekturen. Partitionierung bedeutet die Zerlegung der Gesamtschaltung in leichter prüfbare Teilschaltungen. Die Summe des Aufwandes zur Prüfung der Teilschaltungen ist wesentlich geringer als die zur Prüfung der Gesamtschaltung. Bus-Architekturen machen es möglich durch gezieltes Aktivieren einzelner Teilnehmer am Bus auch die Testbarkeit einfacher zu gestalten.

Strukturierter Entwurf

Das Ziel besteht in der Reduzierung der sequenziellen Komplexität eines Netzwerkes zur Erleichterung der Testsatzgenerierung und Testverifizierung. Durch die Schaffung von Möglichkeiten zur Steuerbarkeit (controllability) und Beobachtbarkeit (observability) der Zustände einer sequenziellen Maschine wird dieses Ziel erreicht. Maßnahmen, die zu diesen Schaltungseigenschaften führen, werden als „passive Testhilfen“ bezeichnet.

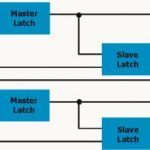

Eine dieser passiven Testhilfen, die sich in den letzten Jahren als systematische Hilfe durchgesetzt hat, und mittlerweile zum Standard bei Herstellern von Großrechnern geworden ist, ist das Scan-Path-Verfahren (SPV). Mittels des SPV können Schaltungen mit sequenziellen Speicherelementen in beobachtbare und steuerbare kombinatorische Schaltungsteile aufgegliedert werden. Dazu ist die Steuerbarkeit und Beobachtbarkeit der internen Zustände der Speicherelemente selbst erforderlich. Erreicht wird das durch Zusammenschaltung der internen Speicherelemente zu Schieberegistern, um das serielle Einschieben von Testmustern und das serielle Auslesen der Testantworten zu ermöglichen. Der Klassiker unter diesen Verfahren ist das LSSD (Level Sensitive Scan Design), das in den 60er Jahren von IBM für Großrechner entwickelt wurde (Bild 4). Es basiert auf der Erweiterung funktioneller Speicherelemente zu Schieberegisterelementen, den „Shift Register Latches“ (SRL).

Im Normalbetrieb arbeitet das SRL als Latch (A=B=0) mit Dateineingang D, Takteingang C und Datenausgang L1. Im Testmodus übernimmt es die Funktion einer Schieberegisterzelle (C=0). Der Schiebedateneingang I wird mit dem Schiebedatenausgang L2 der vorhergehenden Zelle verbunden. Von L2 werden die Daten zu I der nächsten Zelle geschaltet. Die Takteingänge A/Master Clock und die B/Slave Clock werden alternierend gesetzt, und bewirken den Schiebevorgang (Bild 5). Das Scan-Path-Verfahren zeigt am Beispiel des LSSD, dass komplexe sequenzielle Schaltungen in überschaubare rein kombinatorische Schaltungen zerfallen. Da kombinatorische Schaltungen im Gegensatz zu sequenziellen Schaltungen mit wesentlich weniger Testvektoren testbar sind, sind Testaufwand und Testzeit bedeutend geringer.

Bild 5 zeigt, dass die Beispielschaltung in kombinatorische Blöcke zerfällt, die teils von äußeren Leitungen, aber auch – das ist wichtig – von der schaltungsinternen sequenziellen Logik getestet werden. Der Nachteil der sequenziellen Logik wird in den Vorteil ihres Einsatzes als Teil der Testmaschinerie gewandelt.

Anwendung auf Flachbaugruppen

Die logische Weiterentwicklung ist die Anwendung der Erkenntnisse auf Flachbaugruppen, um mit diesen Techniken die Testprobleme zu überwinden. Wenn das Verfahren bisher auf den Schaltkreis zutraf, muss es nun auch auf die Baugruppe transformiert werden. Was wird benötigt?

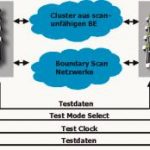

Zwischen den Schaltkreisen braucht man Testzellen, die ebenso als Schiebeketten hintereinander schaltbar, und über wenige Leitungen aussteuerbar und auslesbar sind. Werden diese Testpunkte in den Leitungen angebracht, sind sie Ansteuerpunkte für den In-Circuit-Test. Doch die zunehmende Komplexität der Baugruppen erfordert, diese Testpunkte in die Bauelemente zu integrieren, um zusätzlichen Platz für Netze zu schaffen.

Diese testfreundliche Forderung erfüllt in idealer Weise Boundary Scan/JTAG. Boundary Scan wurde zum standardisierten Test von Bauelementen und ihren Verbindungsnetzwerken entwickelt.

Boundary Scan – Prinzip und Anwendung

Boundary Scan ist das wohl genialste Testverfahren, das ähnlich dem In-Circuit-Test in der Schaltung testet, den Fehlerort aufspürt, Tausende von Testpunkten – wenn es sein muss, auch unter BGAs – setzt und dazu lediglich vier Leitungen braucht. Während der ICT nur mit speziell angefertigten Adaptern testen kann, ist der Boundary Scan Test sinnvoll, wenn sich mindestens ein scanfähiges Bauelement auf dem Board befindet.

Boundary Scan bedeutet soviel wie „Testen in der Peripherie (at boundaries) eines Schaltkreises“. Neben der Kernlogik (Core Logic) und den Kontaktpunkten des ICs wird in einen Schaltkreis zusätzliche Logik eingefügt. Diese Testpunkte werden zwischen Kernlogik und den physikalischen Pins des Schaltkreises integriert. Die folgende Abbildung verdeutlicht dies grafisch – im Vergleich dazu das Prinzip des IC-Tests (Bild 6 + 7).

Boundary Scan lässt sich einfach und universell adaptieren. Generell kann man sagen, dass die Unterstützung des Produktes über seinen gesamten Lebenszyklus erfolgt. Bereits in der Designphase sind mittels der CAD-Daten Tests möglich, welche sogar später noch – selbst bis hin zum Einsatz beim Kunden – genutzt werden können. Das bedeutet auch, dass Testpattern, die bereits für die Design-Verifikation erstellt wurden, für den Prototypen-Debug und Fabrikationstests übernommen werden. Dies ist ein wichtiger Vorteil, da gerade bei der Entwicklung hochkomplexer Baugruppen deren spätere Testbarkeit mit eingeplant werden sollte. Damit reduziert sich der Testaufwand erheblich. Darüber hinaus reduzieren sich Diagnosezeiten auf ein Minimum.

Zusammenfassung

Design for Testability – Boundary Scan ist dafür wie geschaffen. Kein anderes Testverfahren beruht derart auf dem Design. Was jetzt problematisch klingt, ist aber heutzutage ein Standard. Denn alle großen Hersteller von Bauelementen haben die Boundary Scan Architektur prinzipiell in ihren ICs integriert. Gerade im Hinblick auf die zunehmende Komplexität der Boards – und logischerweise auch der Bauteile selbst (BGA, µBGA, FlipChip) – ist Boundary Scan die einzige Konsequenz im Hinblick auf Testbarkeit und Testabdeckung. „Designed to make a difference“ ist der Werbeslogan eines großen Industrieanbieters. Im Falle von Boundary Scan trifft das wie bei keiner anderen Testtechnologie zu. Man muss sie nur noch anwenden.

EPP 473

Unsere Webinar-Empfehlung

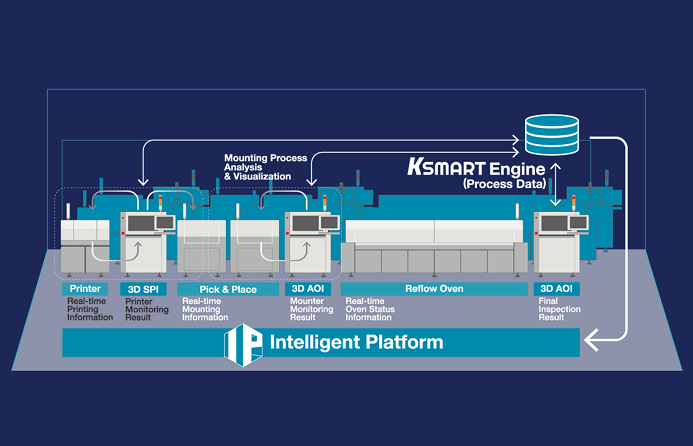

Die Nutzung der 3D-Mess- und Prozessdaten bringt die Produktionssteuerung auf die nächste Stufe. Echte 3D-Messung ermöglicht KI-basierte Prozessmodellierung zur Vorhersage von Parameteränderungen und -defekten oder zur Ursachenanalyse bis hin zu einzelnen Werkzeugen und Best…

Teilen: