Das englische Unternehmen Ubiquisys hat eine Mobilfunk Femtozelle namens ZoneGate entwickelt, die eine kostengünstigere Kommunikation, eine bessere Versorgung und neue Dienste ermöglichen soll. Die Serienproduktion der Femtozelle erfolgt durch den Fertigungsdienstleister Sony UK Technology Centre (Sony UK Tec) in Großbritannien. Ubiquisys setzt bei diesem Produkt auf eine weitgehende Kompatibilität zu Standards, wie etwa der Unterstützung von GAN, IMS und dem künftigen Iuh-Protokoll von 3GPP. Gängige Standards, wie Ethernet oder ADSL-Breitbandsysteme, kommen auch bei der Verbindung zum jeweiligen Netzbetreiber zum Einsatz.

Das Management der Femtozelle erfolgt entsprechend dem Industriestandard TR-069. Und durch die Verwendung von Standard Netzwerk Timing-Protokollen wird zudem eine problemlose Timing-Synchronisation mit den Produkten anderer Hersteller sichergestellt. Es gibt allerdings eine Reihe von Herausforderungen, um ein derartiges Produkt erfolgreich auf dem Massenmarkt positionieren zu können. Hierzu gehören neben einer einfachen Installation und kognitiven Funkverfahren, um Interferenzen bei einem Einsatz im großen Stil vermeiden zu können, auch entsprechende Design-for-Test-Maßnahmen und eine kostengünstige Fertigung.

Design-Übersicht

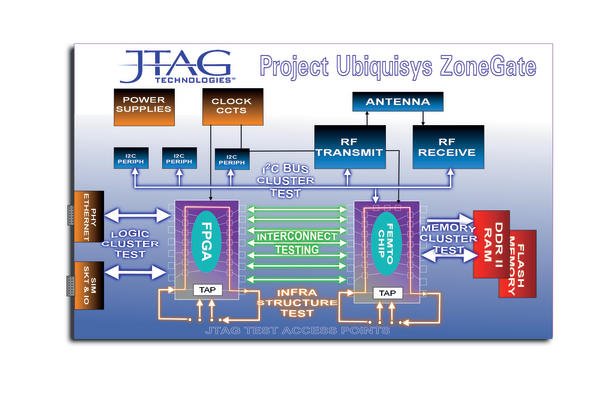

ZoneGate besteht nur aus einer einzigen Baugruppe, welche die RF-Schaltung, die Basisband-Verarbeitung, die Takt-Schaltungen und Stromversorgung enthält. Durch eine sorgfältige Bauteilauswahl und Layout konnte Ubiquisys die Verlustleistung des Designs soweit reduzieren, dass auf eine Kühlung durch Lüfter verzichtet werden konnte und ein lautloser Betrieb möglich ist, ohne dass aber Kompromisse hinsichtlich der Zuverlässigkeit erforderlich sind. Die Basisband-Verarbeitung erfolgt durch einen kundenspezifischen Femtozellen-Chip und ein FPGA, zudem ist als Speicher ein DDR2-SDRAM- und ein Flash-Chip enthalten. Insgesamt umfasst das Mixed-Signal-Design rund 1.000 Knoten, wobei die überwiegende Mehrzahl mit digitalen BGA-Bauteilen (Ball Grid Array) verbunden ist – das größte Bauteil ist ein 27 x 27 mm großer BGA-Chip.

Die Testaspekte

Auf Grund der BGA-Bauteile erwies sich ein struktureller Test mittels eines In-Circuit-Testers (ICT) und einem konventionellen Nadelbett-Adapter als nicht durchführbar. Die hierzu notwendigen ICT-Testpunkte würden die Baugruppenfläche deutlich vergrößern. Außerdem würden solche Punkte zu Problemen bei der Signalintegrität führen und haben sich auch im RF-Bereich der Baugruppe als unpraktisch erwiesen. Um die Kosten in Grenzen halten zu können, wurde nach einer Testlösung gesucht, die einerseits skalierbar, andererseits aber auch (re-)konfigurierbar ist, um flexibel auf Änderungen im Baugruppen-Design bei der Weiterentwicklung des Produkts reagieren zu können. Durch die Skalierbarkeit kann die Kapazität der Produktion und der Testlinie entsprechend dem jeweiligen Bedarf angepasst werden. Ein Funktionstest allein kann keine hinreichende Fehlerabdeckung und die erforderliche Fehlerauflösung im digitalen Bereich gewährleisten, die notwendig ist, um den Fertigungsprozess überwachen zu können. Ubiquisys entschied sich daher für eine Teststrategie, die einen Funktionstest der RF-, Analog- und Leistungskomponenten mit einem Boundary-Scan-Test der digitalen Schaltungsteile kombiniert. Als Systemanbieter für die Boundary-Scan-Lösung wurde JTAG Technologies ausgewählt.

Die ZoneGate Baugruppe verfügt über zwei Boundary-Scan-Testzugänge (TAPs), einen für das FPGA und einen für den Femtozellen-Chip (Bild 1). Mit den Boundary-Scan-Ketten um diese beiden Bauteile herum lassen sich nicht nur ein Test der Verbindungen (rund 60 % aller Netze der Karte), sondern auch ein Cluster-Test der Logik- und Speicherschaltungen auf der Baugruppe durchführen. Durch die Simulation der Schreib- und Lesezyklen der Speicherblöcke können mit diesem Cluster-Test Unterbrechungen und Kurzschlüsse auf den Adress- und Datenleitungen erkannt werden.

Für den Test der anderen Nicht-Boundary-Scan-Bauteile ist meist eine Simulation von Protokollen erforderlich, wie beispielsweise I2C, SPI oder von einfachen parallelen Bustransfers. Damit lassen sich dann die Register innerhalb der Bauteile auslesen oder beschreiben oder sogar die Funktion des Bauteils vollständig oder teilweise testen. Durch die Einbettung von Cluster-Testprotokollen in die Modelle lässt sich die Generierung der Cluster-Tests mittels der JTAG ProVision Software automatisieren. Zudem sind die Modelle von Design zu Design wiederverwendbar.

Diese Kombination von Boundary-Scan- und Funktionstest ergibt eine effiziente Testlösung für die Fertigung, die Ubiquisys gemeinsam mit dem Fertigungsdienstleister Sony UK Tec erstellt hat. Entscheidend für eine erfolgreiche Teststrategie ist allerdings auch eine minimale Verzögerung zwischen Produktion und Test, so dass Fehler im Fertigungsprozess frühzeitig erkannt werden können und zwar bevor zu viel Ausschuss produziert wird. Die Produktions- und Testlinien von Sony UK Tec laufen damit praktisch parallel.

Die Testlösungen von Sony UK Tec sind deshalb auch in die Steuerungssoftware der Fertigungslinien integriert. Der Boundary-Scan-Test erfolgt mit Hilfe von PXI-Controllern von JTAG Technologies. Dadurch lassen sich mehrere Produkte gleichzeitig testen, wobei die Testergebnisse für das Bedienpersonal jeweils angezeigt werden. Das Testprogramm erlaubt eine Diagnose der Fehler bis auf Knoten- oder Bauteilebene. Zudem werden alle Ergebnisse in einer Datenbank für eine spätere statistische Analyse gespeichert.

Die beiden Unternehmen haben bei der Entwicklung der Testfolgen eng zusammengearbeitet, wodurch eine hohe Fehlerabdeckung beim Funktionstest erreicht werden konnte und sich nun auch Bauteile testen lassen, die keine Boundary-Scan-Schnittstelle haben. Selbst mit den zwei TAPs benötigt die Boundary-Scan-Schnittstelle nur wenige zusätzliche Pins auf dem Produkt, über die viele Bauteile und Funktionen getestet werden können. Damit steht eine kostengünstige Möglichkeit zur Implementierung von Funktionstests in der Fertigungslinie zur Verfügung, wobei die Testlinie auch die erforderlichen Taktzeiten einer Fertigung mit hohen Stückzahlen einhalten kann.

electronica, Stand A1.221

EPP 440

Unsere Webinar-Empfehlung

10.10.22 | 10:00 Uhr | Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine…

Teilen: