Der In-Circuit-Test (ICT) zählt schon jahrzehntelang zu den bewährten Prüfmethoden, was auch durch die große Anzahl von täglich ICT-getesteten Baugruppen bestätigt wird. Höhere Integrationsdichten und mangelnder Prüfnadelzugriff konnten zum Teil durch Verfahren wie Boundary Scan [IEEE01, IEEE99, IEEE03, Park89, Park03a] kompensiert werden. In vielen Fällen kann aber nicht auf einen elektrischen ICT verzichtet werden. Der folgende Artikel beschreibt eine Methode, wie auch künftig eine hohe Prüfabdeckung im ICT erreicht werden kann.

Der In-Circuit-Test erfordert einen direkten Leiterplattenzugriff über einen „Nadelbettadapter” (Bild 1). Das Testsystem verbindet – gesteuert durch das Testprogramm – die Prüfnadeln nacheinander mit den benötigten Ressourcen (beispielsweise Spannungsquelle oder Stromquelle), und führt die gewünschten Messungen durch. Das kann im einfachsten Fall eine simple Zweidraht-Widerstandsmessung sein, im Extremfall aber auch ein komplexer Digitaltest (gegebenenfalls auch ein Boundary-Scan-Test), für den Hunderte von digitalen Treibern und Komparatoren von einem Digitaltest-Sequencer konfiguriert werden. Der Testzugriff kann aus mehreren Gründen begrenzt sein. Die Wichtigsten davon sind:

- 1. Hohe Bauteil-, Anschluss- und Leiterbahndichte.

- 2. Leiterbahnen im Inneren einer Multilayer-Platine, die keine Verbindung zu einer der außenliegenden, kontaktierbaren Leiterbahnen haben.

- 3. Unmöglichkeit, an kritischen Stellen der Leiterplatte Testpunkte vorzusehen, weil diese die Signalintegrität beeinträchtigen würden, das Thema des vorliegenden Beitrags.

Kontaktieren von Leiterplatten

Die Design-Regeln für In-Circuit-Testpunkte ergeben sich daraus, dass auf jeder Leiterplatte ein paar hundert oder tausend Punkte zuverlässig kontaktiert werden müssen. Ein Testadapter muss dies während seiner Lebensdauer viele tausend Mal problemlos ermöglichen. Wenn auch nur ein einziger Kontakt ausfällt, kann die Leiterplatte eventuell nicht getestet werden oder – schlimmer noch – der Test liefert ein fehlerhaftes Ergebnis. Dies gab den Anlass zur Entwicklung von Industriestandards für den Entwurf von Leiterplatten, die sich problemlos kontaktieren lassen („Design for Probeability”).

Prüfnadeln kann man sich als kleine Pfeile vorstellen, die auf bestimmte Punkte der Leiterplatte zielen. Bullock [Bull87] hat Regeln dafür aufgestellt, wie solche Zielpunkte beschaffen sein müssen – seien es Testpunkte, die speziell zum Kontaktieren vorgesehen wurden oder andere gegebene Ziele, die ohnehin vorhanden sind. Eines dieser Ziele, das sich in vielen Fällen anbietet, ist eine Durchkontaktierung, die verschiedene Layer einer Multilayer-Leiterplatte miteinander verbindet. „Leider” (unter Testaspekten) werden sowohl die Abmessungen der Bauteile und Anschlüsse, als auch die Breite der Leiterbahnen mit jeder Produktgeneration kleiner – und damit auch die Ziele für die Prüfnadeln. In der Praxis gibt es eine untere Grenze für die Abmessungen der Zielpunkte, unterhalb derer die Prüfnadel das Ziel nicht mehr zuverlässig trifft. Laut Bullock können runde Ziele mit einem Durchmesser ab 35 mil (0,89 mm) als zuverlässig angesehen werden. Andere Testexperten setzen die Untergrenze bei nur 26 mil (0,66 mm) an, dies allerdings zu Lasten wesentlich höherer Kosten und einer wesentlich geringeren Kontaktierungszuverlässigkeit. Man beachte, dass ein rundes Ziel mit einem Durchmesser von 35 mil eine Fläche von 962 mil2 hat, und ein SMT-Bauteil der Größe 0204 eine Fläche von 800 mil2. Ein Testpunkt kann demnach eine größere Fläche als ein Bauteil beanspruchen. Es kommt noch erschwerend hinzu, dass die Breiten und Abstände von Leiterbahnen mit definiertem Wellenwiderstand fest vorgegeben sind, und exakt eingehalten werden müssen. Bei modernen Hochgeschwindigkeits-Designs betragen die Leiterbahnbreiten und -abstände oft nur noch 3 mil (0,076 mm). Datenübertragungsraten im Gigabit-Bereich erlauben für diese Parameter nur sehr enge Toleranzen. Wohl kaum ein Entwickler wird sich dazu überreden lassen, einen 35-mil-Testpunkt auf einer nur 3 mil breiten Leiterbahn unterzubringen.

Leiterplatten-Design-Regeln für Hochgeschwindigkeitssysteme

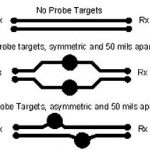

Leiterplatten-Design-Regeln für Hochgeschwindigkeitssysteme stellen den Entwickler beim Layout vor ganz neue Herausforderungen. So müssen z.B. unsymmetrische Wellenleiter bestimmte Werte für Breite, Dicke, Höhe über einer Masseebene sowie Maximalabstand zu Masseleiterbahnen im gleichen Layer einhalten. Auch für die Dielektrizitätskonstante des Leiterplattenmaterials gelten enge Toleranzen. Das Ergebnis ist ein definierter Wellenwiderstand, üblicherweise im Bereich von 28 bis 100 Ohm. Die Rambus-Layout-Regeln (Bild 2) ergeben einen Wellenwiderstand von 28 Ohm. Obwohl dieser kleine Wellenwiderstand eine relativ große Leiterbahnbreite bedingt, ist diese dennoch nur etwa halb so groß wie der empfohlene Testpunkt-Durchmesser. Würde man auf einer solchen Leiterbahn einen runden 35-mil-Testpunkt anbringen, so ergäbe sich an dieser Stelle eine erheblich größere Kapazität nach Masse, und ein entsprechend kleinerer Wellenwiderstand. Dieser Impedanzsprung würde Reflexionen verursachen, und dadurch die Signalqualität beeinträchtigen. Testpunkte verursachen noch ein weiteres Problem: sie erzwingen unerwünschte Biegungen der Leiterbahnen und eine Änderung des Leiterbahnabstands. Im Idealfall sehen differenzielle Leiterbahnen etwa so aus wie in Bild 3, oben. Der Abstand der Leiterbahnen ist für den Wellenwiderstand eines Differenzialpaares von ausschlaggebender Bedeutung. Nehmen wir als Beispiel den neuen Hochgeschwindigkeitsbus-Standard PCI Express (www.pcisig.com/specifications), der für Differenzialpaare eine Leiterbahnbreite und einen Leiterbahnabstand von jeweils 5 mil spezifiziert; daraus resultiert ein Differenzialpaar-Wellenwiderstand von 100 Ohm.

Wenn wir Testpunkte vorsehen, sind wir gezwungen, die Leiterbahnen an diesen Stellen auseinander zu spreizen und zu verbiegen – entweder symmetrisch (Bild 3, in der Mitte) oder unsymmetrisch (Bild 3, unten). Durch das Aufspreizen kann sich der Wellenwiderstand leicht auf 120 Ohm erhöhen. Der Abstand zwischen den Testpunkten entspricht dem von Bullock [Bull87] empfohlenen Mindestabstand von 50 mil, der sich aus den Abmessungen der Prüfnadeln ergibt. Das Problem vervielfacht sich, wenn Testpunkte auf zahlreichen, parallel zueinander verlaufenden Differenzialpaaren angebracht werden. Jeder zusätzliche Testpunkt erfordert Biegungen und Abstandsänderungen, nicht nur bei den unmittelbar betroffenen Leiterbahnen, sondern auch bei den benachbarten. Diese Unregelmäßigkeiten in den Signalpfaden rufen bei Entwicklern große Besorgnis hervor. Sie haben das Gefühl, dass sie für die Testfreundlichkeit ihrer Baugruppen erhebliche Design-Risiken auf sich nehmen müssen.

Lassen sich die Probleme durch Boundary Scan lösen?

Ein großer Vorteil des Boundary-Scan-Testverfahrens besteht darin, dass es die Anzahl der Testpunkte, die direkt kontaktiert werden müssen, drastisch reduziert. Vereinfacht ausgedrückt: der Boundary-Scan-Test verlagert die Testpunkte an die Außenränder der Chips. Bei Designs, die den IEEE-Standard 1149.4 [IEEE99] unterstützen, lassen sich sogar zahlreiche diskrete analoge Bauelemente ohne direktes Kontaktieren testen.

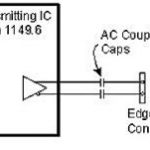

Der neue IEEE-Standard 1149.6 [IEEE03, EBP03] unterstützt auch das Testen neuartiger I/O-, Differenzial- und AC-gekoppelter Strukturen, wie sie jetzt immer öfter auf den Leiterplatten zu sehen sind. Sind dadurch zusätzliche Testpunkte überflüssig geworden? Das ist leider nicht der Fall. Betrachten wir eine Baugruppe, beispielsweise ein PCI-Express-System, bei der einige Hochgeschwindigkeits-ICs den Standard 1149.6 unterstützen. PCI Express arbeitet mit differenzieller Datenübertragung und AC-Kopplung. Die Design-Regeln schreiben vor, dass der Koppelkondensator sich auf der Treiberseite des Übertragungspfades befinden muss. Oft befinden sich ein PCI-Treiber und der zugehörige Empfänger auf verschiedenen Leiterplatten. In Bild 4 ist eine Leiterplatte skizziert, die ein Beispiel für eine solche Konstellation darstellt.

Wenn ein Testsystem die „1149.6-Fähigkeit” des Designs nutzen will, muss es auf die beiden differenziellen Signale zugreifen können. Dies könnte man erreichen, indem man das Testsystem über einen passenden Steckverbinder1 an den Kartenrandsteckverbinder des Testobjekts anschließt. Allerdings sind die meisten In-Circuit- und Boundary-Scan-Testsysteme nicht in der Lage, AC-gekoppelte Signale direkt zu verarbeiten. Aus diesem Grund benötigt man eine für die Erfassung solcher Signale geeignete Testadapterelektronik. Wenn ein In-Circuit-Testsystem direkten Zugriff auf den Bereich der Leiterbahnen zwischen dem Treiberausgang und den Koppelkondensatoren hätte, könnte es die pulsierenden Gleichspannungen auf den beiden Leiterbahnen erfassen. In einem zweiten Test2 könnte das In-Circuit-Testsystem die beiden Schaltungsknoten stimulieren, um die Kondensatoren und die Steckverbinderanschlüsse zu überprüfen. Als Testingenieure hätten wir deshalb nur zu gern direkten Zugriff auf die beiden Leiterbahnen. Die Frage ist: Wie können wir unsere Kollegen in der Entwicklung dazu bringen, dort Testpunkte vorzusehen? Und natürlich nicht nur dort, sondern auch noch an zahlreichen anderen Stellen. Es muss eine Möglichkeit gefunden werden, das zu realisieren, ohne die Entwicklungsarbeit dadurch wesentlich zu erschweren oder das Design-Risiko zu vergrößern.

Kontaktierung einmal „anders herum“

Der Nadelbettadapter ist seit Jahrzehnten mit dem In-Circuit-Test scheinbar untrennbar verbunden. Wir haben auch gelernt, wie man es erreicht, dass Tausende von Prüfnadeln Tag für Tag exakt ihr Ziel treffen.

Aber warum sollte man das Prinzip nicht einmal „auf den Kopf stellen”? Was wäre, wenn die Leiterplatte irgend eine Art von Prüfnadel enthielte, und der Testadapter deren Ziel wäre? Stellen Sie sich einen Augenblick lang vor, Sie könnten auf Ihrer Leiterplatte eine Prüfnadel anbringen, und Ihr Testadapter enthielte einen 35-mil-Zielpunkt. Die Genauigkeitsanforderungen und zulässigen Toleranzen wären die gleichen wie bisher – damit gäbe es also keine Probleme. Im Prinzip könnte das funktionieren. Die Frage ist: Wie bringt man eine Prüfnadel auf der Leiterplatte an, und zwar so, dass sie deren elektrischen Eigenschaften möglichst wenig beeinflusst? Und natürlich soll das Ganze auch kostengünstig und zuverlässig sein und reproduzierbare Ergebnisse liefern.

Die Lösung: Test-Lotperlen

Ein zusätzliches Bauteil auf der Leiterbahn anzubringen, das nicht breiter ist als die Leiterbahn selbst, wäre schwierig. Problemlos machbar ist hingegen ein kleiner Lothöcker mit halbkugelförmigem Querschnitt, den wir „Test-Lotperle” (bead probe) getauft haben. Diese Lotperle würde auf einer Leiterbahn liegen; sie hätte die gleiche Breite wie die Leiterbahn selbst und eine Länge, die etwa dem Drei- bis Fünffachen der Leiterbahnbreite entspricht. Sie wäre nur ein paar mil hoch und würde ein paar mil über die benachbarte Lötstoppmaske hinausragen.

1. Lotperle auf der Leiterplatte und Zielpunkt im Testadapter

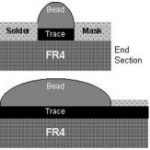

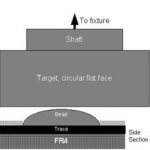

Bild 5 zeigt Stirnseiten- und Seitenquerschnitte einer Lotperle. Die Perle hat folgende Abmessungen: Breite gleich Leiterbahnbreite, Höhe gleich 50% bis 100% der Leiterbahnbreite, Länge gleich drei- bis fünffache Leiterbahnbreite. Die Test-Lotperle ragt ein wenig über die Lötstoppmaske hinaus, die typischerweise eine Dicke von nur ein oder zwei mil hat. Das im Testadapter angebrachte Gegenstück zur Test-Lotperle ist ein runder, gefederter Stift mit Waffelmuster-Kopf, wie er bei herkömmlichen In-Circuit-Testadaptern häufig zum Kontaktieren der Zuleitungsdrähte bedrahteter Bauteile verwendet wird, nur dass er jetzt als Zielpunkt dient (Bild 6).

Aus zwei Gründen ist die Lotperle länger als breit. Erstens ergibt sich dadurch eine etwas größere Haftfläche auf der Leiterbahn. Zweitens ist dadurch auch bei einem etwas gröberen Waffelmuster auf dem Federstiftkopf gewährleistet, dass der Kopf die Lotperle an mehreren Stellen kontaktiert. Wie bei der herkömmlichen In-Circuit-Kontaktierung treten auch bei diesem Verfahren unvermeidliche Positionierfehler (horizontale Verschiebung zwischen Lotperle und Stift) auf. Diese sind jedoch nicht größer als bei herkömmlicher Kontaktierung und daher beherrschbar.

2. Herstellung einer Test-Lotperle

Test-Lotperlen lassen sich im ganz normalen Leiterplatten-Lötprozess herstellen. Hierzu wird an der Stelle der Leiterbahn, an der die Lotperle entstehen soll, die Lötstoppmaske entsprechend ausgespart. Die Breite der Aussparung kann etwas größer als die Leiterbahnbreite sein; wenn das Lot nach dem Aufschmelzen wieder fest wird, zieht es sich durch Oberflächenspannung bis auf die Breite der Leiterbahn zusammen. Dadurch verbleibt um die Lotperle herum eine „Rinne”, in der sich Flussmittel sammeln kann. Die Länge der Aussparung in der Lötstoppmaske bestimmt die Gesamtlänge der Lotperle. Somit bestimmen die Leiterbahnbreite und die Länge der Aussparung in der Lötstoppmaske die Abmessungen der Lotperle.

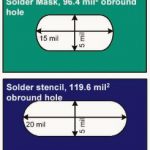

Die Höhe der Lotperle wird durch zwei Faktoren bestimmt. Erstens besteht eine typische Lotpaste zu etwa 50%-Volumenprozent aus Flussmittel, das beim Reflow-Löten verdampft. Das bedeutet, dass rund die Hälfte des Pastenvolumens als Lotperle übrig bleibt. Die Lötstoppmaske wird absichtlich etwas breiter als die gewünschte Breite der Lotperle gemacht, damit so viel Lot aufgebracht wird, dass sich beim Erkalten durch die Oberflächenspannung die gewünschte Höhe ergibt. Bild 7 zeigt ein typisches Beispiel für die Lötstoppmaske, die Lotpastenschablone und die resultierende Lotperle. Man beachte, dass die Fläche der Lotpastenschablone etwas mehr als das Doppelte der Fläche des freiliegenden Leiterbahnabschnitts beträgt (119,6/45 = 2,33); beim Verdampfen des Flussmittels reduziert sie sich auf etwa das 1,16fache. Dadurch ergibt sich nach dem Reflow eine Lotperlenhöhe von etwa dem 1,2fachen der Dicke der Schablone (Fortsetzung in der Ausgabe 3-4/2005).

EPP 472

Fußnoten

- 1 In der Großserienproduktion sucht man das zu vermeiden, weil das automatische Einstecken eines Steckverbinders sich nur schlecht (bzw. mit großem Aufwand) automatisieren lässt.

- 2 Für diesen Teil des Tests würde man zweckmäßigerweise einen kapazitiven Testadapter, wie z. B. TestJet verwenden. Bei diesem Test würden die Koppelkondensatoren gleich mitgetestet. Ein Gegenstück zum Kartenrandsteckverbinder des Testobjekts wird für diesen Test nicht benötigt.

Unsere Webinar-Empfehlung

Die 3D-Messung und Inspektion des Lotpastendrucks ist ein wichtiges Qualitätswerkzeug. Dieses funktioniert nur mit den richtigen Toleranzen und Eingriffsgrenzen.

Teilen:

.png)