Die Zeiten der klassischen Durchstecktechnik (THT) bei den Bauformen sind vorbei. Längst wurden diese durch die wesentlich kleineren „Surface Mounted Devices“ (SMD) abgelöst. Doch auch hier machte die Entwicklung nicht Halt. Der Markt verlangte nach immer kleineren, kompakteren Bauformen. So sieht man sich heute konfrontiert mit Ball-Grid-Arrays (BGAs), Flip-Chip und Chip-On-Board (COB) Packages.

Mario Berger, Göpel electronic, Jena, Deutschland

Dieser Trend ist natürlich nicht spurlos an den einzusetzenden Teststrategien vorbeigegangen. Wo man bei der Durchstecktechnik noch nicht einmal ansatzweise Probleme beim Setzen von für den Incircuit-Test benötigten Testpunkten hat und die Sichtkontrolle als völlig ausreichend gilt, stößt man bei Baugruppen in SMD-Technik mit diesen Methoden bereits an Grenzen. Die Messlatte aber wandert durch die erwähnten neuen Bauformen stetig nach oben. Gibt es überhaupt noch Teststrategien, die den großen Anforderungen gewachsen sind?

Eine Teststrategie von heute

Die Teststrategien, welche man aktuell in den Fertigungsstätten hierzulande antrifft, basieren weitestgehend auf der Philosophie des jeweiligen Unternehmens. In begrenztem Maße spielt auch das herzustellende Produktspektrum eine gewisse Rolle, obwohl es auf die Wahl der eingesetzten Testsysteme kaum Einfluss hat. Hier zählen eher Kriterien wie Losgrößen und Anzahl an Produktvarianten. Als Entscheidungskriterium für die Anschaffung und den Einsatz eines Testsystems gewinnen Flexibilität oder aber die Testgeschwindigkeit, sprich der Durchsatz, an Bedeutung. Die Testabdeckung, also die Fähigkeit eines Testsystems eine gewisse Anzahl an Fehlern detektieren zu können, spielte bei der Auswahl der Testsysteme eine eher geringere Rolle.

Jedem ist der Vorteil eines Automatischen Optischen Inspektionssystems (AOI) gegenüber seiner Alternative, der manuellen Sichtkontrolle, klar. Da verwundert es nicht, dass ein solches System fester Bestandteil heutiger Teststrategien ist. Ebenso bekannt sind auf Seiten des elektrischen Testens die Vorzüge des Incircuit Tests (ICT), der nach wie vor eine führende Rolle in der Teststrategie von heute spielt. Allerdings hält sein bewegliches Pendant, der Flying Prober (FP), aufgrund der wesentlich höheren Flexibilität mehr und mehr Einzug in die Fertigungshallen der Unternehmen.

Aufgrund dieser Tatsachen gestaltet sich die Skizzierung einer Teststrategie von heute als recht einfache Aufgabe. Das Ergebnis ist in Bild 1 und Bild 2 ersichtlich und wird im Folgenden näher beschrieben.

Der erste optische Test findet bereits nach dem Lötpastendruck statt und überprüft die Schablone des Lötpastendruckers auf mögliche Verstopfungen. Da hierfür keine großen Genauigkeiten benötigt werden, genügt ein recht einfaches AOI, welches oftmals Bestandteil des Lötpastendruckers selbst ist.

Als nächster optischer Test erfolgt typischerweise nach dem Bestücken eine stichprobenartige Sichtkontrolle. Ziel ist es, die Platzierung der Bauteile zu überwachen und gegebenenfalls den Bestückautomaten nachzujustieren bzw. den Bestückprozess zu optimieren. Eine lückenlose Qualitätskontrolle ist hiermit nicht möglich, da es sich um einen stichprobenartigen Test handelt. Der Schwerpunkt der optischen Qualitätskontrolle liegt somit in der nach dem Lötprozess angesiedelten AOI. Sie überwacht Bauteile u. a. auf Anwesenheit, Lagerichtigkeit oder untersucht sichtbare Lötstellen.

Im Gegensatz zur optischen Qualitätskontrolle finden die elektrischen Tests im Prüffeld und nicht in der Produktion statt. Derzeit werden hauptsächlich Incircuit-Tester bzw. Flying Prober eingesetzt. Diese überprüfen die Bauteile auf die Einhaltung der angegebenen elektrischen Parameter sowie auf deren Funktion im Einzelnen. Gleiches gilt für die Leiterbahnen. Alles in allem können mit diesem ersten Test 90 % der elektrischen Fehler nachgewiesen werden.

Als Ergänzung folgt im nächsten Schritt möglicherweise ein Funktionstest. Hier wird die Baugruppe zum ersten Mal in ihrem simulierten, späteren Arbeitsumfeld eingeschaltet. Mit diesem Test werden somit alle für die Funktion der Baugruppe relevanten Bauteile und Leiterbahnen auf ihre korrekte Funktion überprüft. Ein einfacher Funktionstest kommt somit auf eine Testabdeckung von schätzungsweise 40 %.

Es lässt sich also feststellen, dass mit elektrischen Tests (ICT, FPT) eine Testabdeckung von fast 100 % erreichbar ist. Der Funktionstest bringt bei einem aufwändigen Incircuit-Test kaum einen Zugewinn in puncto Testabdeckung.

Was kann man also über die Teststrategie von heute sagen? Sie ist klar definiert und zumeist von der Firmenphilosophie geprägt. Die mit den beiden überragenden Testverfahren AOI und ICT erzielbaren hohen Testabdeckungen tragen dazu bei, dass man sich kaum Gedanken darüber machen muss, welches Testverfahren für den optischen Test und welches für den elektrischen Test am geeignetsten bzw. am wirtschaftlichsten ist.

All das bedingt aber zweierlei Gegebenheiten. Erstens setzt eine 100%ige Testabdeckung der Automatischen Optischen Inspektion voraus, dass jedes Bauteil mit jedem Anschlusspin, somit jede einzelne Lötstelle sichtbar ist. Zweitens setzt die nahezu 100%ige Testabdeckung des Incircuit-Testverfahrens voraus, dass jede einzelne Leiterbahn über einen Testpunkt adaptierbar ist.

Aber genau diese beiden Punkte werden mit den in immer neuen Varianten auf den Bauteilmarkt drängenden modernen Bauformen wohl nicht mehr realisierbar sein. Doch schauen wir uns diese zunächst einmal an.

Moderne Bauformen

Der Trend zur Miniaturisierung hält weiter an und bringt bei den integrierten Schaltkreisen heute schon Bauformen hervor, welche auf die Größe des Chips (des Dies) reduziert sind. Da gilt ein „Quad-flat no-lead (QFP)“-Gehäuse mit seinen bis zu 16 Anschlüssen und Außenmaßen von 3 x 3 mm Kantenlänge fast schon als Riese. Ein heutiges „Ball-Grid-Array (BGA)“-Gehäuse erlaubt beispielsweise den Anschluss von mehr als 1700 Leiterbahnen bei einer Kantenlänge von gerade einmal 42 x 42 mm. Eine weitere moderne Bauform ist der „Chip-On-Board (COB)“, bei dem der Chip direkt auf der Leiterplatte befestigt und die Anschlüsse gebondet werden. Doch es geht noch kleiner, nämlich ohne Bond-Drähte und stapelbar, indem man den Chip in die Leiterplatte integriert. An manchen Stellen taucht dann diesbezüglich der Begriff „Chip-In-Board (CIB)“ auf. Und auch hier wird die Entwicklung in naher Zukunft weiter voranschreiten (Stichwort „Nanotechnologie“).

Wohin die Reise gehen wird, ist somit klar. Doch wird dies Auswirkungen auf die Teststrategie von heute haben oder nicht? Das Problem, vor dem ein AOI-System bei einem BGA-Gehäuse steht, ist offensichtlich. Die Anschlusspins sind „von oben“ eben nicht sichtbar. Die Testabdeckung bei einer solchen Bauform sinkt damit dramatisch auf unter 1 % in puncto Anwesenheit und Lagerichtigkeit – von der Lötstellenkontrolle ganz zu schweigen.

Doch auch auf dem Gebiet des elektrischen Testens spielen sich ähnliche Szenarien ab.

Der Incircuit-Test arbeitet bekanntermaßen über eine mechanische Adaption der einzelnen Leiterbahnen, welche über Nadeln realisiert wird. In Bild 3 ist solch ein Aufbau ersichtlich.

Damit die Prüfnadeln die Leiterbahnen adaptieren können, müssen diese mit Testpunkten versehen werden, an denen die Nadeln aufsetzen. Für das nachstehende Beispiel wird nun angenommen, dass ein einzelner dieser Testpunkte eine Fläche von ca. 1 mm² benötigt (die Landefläche selbst ist kleiner, allerdings werden um die Testpunkte herum bestimmt Freistellungsräume benötigt, weswegen die notwendige Fläche eher über der Annahme von 1 mm² liegen wird). Bild 3 zeigt das Verhältnis zwischen den Flächen, welche durch jeweils unterschiedliche 16-polige Bauteile und die erforderlichen Testpunkte zur Kontaktierung aller Bauteilpins benötigt werden.

Für ein „Dual-Inline Package (DIP)“ sieht das Verhältnis zwischen der benötigten Fläche für die Testpunkte zur Fläche für das Bauteil mit 10 % noch relativ gut aus. Bei „Small Outline (SO)“- und „Shrink Small Outline Package (SSOP)“-Bauformen wird schon wesentlich mehr Fläche auf der Leiterplatte für das Testen (Landeflächen) benötigt als für die Funktion (Bauteil). Wirklich dramatisch fällt die Analyse allerdings beim QFN-Gehäuse aus: Hier muss man fast zwei Mal mehr Fläche für das Testen des Bauteils zur Verfügung stellen, als dieses selbst überhaupt benötigt. Die Testverfahren, welche auf einer rein mechanischen Adaption der Leiterbahnen basieren, werden offensichtlich bei solchen modernen Bauformen wirtschaftlich nicht mehr zu vertreten sein. Ganz zu schweigen von dem Versuch die 1700 Bauteilpins eines BGA-Gehäuses zu adaptieren.

Trübe Aussichten oder Herausforderung? Oder gar eine Chance sich am Markt noch besser zu positionieren? Längst gibt es verschiedene neue Testsysteme, die alle auf ihre spezielle Art und Weise die oben geschilderten Probleme mit den neuen Bauformen angehen. Im Folgenden sollen die zwei wohl wichtigsten einmal kurz vorgestellt werden.

Grenzen überwinden mit modernen Testverfahren

Als Alternative zum fehlenden „freien Blick“ auf die Lötverbindungen bietet sich die Röntgeninspektion an. Sie ermöglicht die qualitative Bewertung sämtlicher Lötstellen – ob sie nun frei zugänglich sind wie bei einem SO-Bauteil oder unter einem BGA-Gehäuse liegen. Allerdings muss man an dieser Stelle ganz klar zwischen den Möglichkeiten eines 2D-Röntgensystems und einem 3D-System unterscheiden. So stellt eine beidseitig bestückte Leiterplatte das 2D-System vor eine unlösbare Aufgabe. Auch gibt ein 2D-System keine absolute Garantie für eine untersuchte Lötverbindung. Viele Systeme sind noch nicht in der Lage einen vom BGA-Bauteil beim Lötprozess abgelösten Ball zu detektieren. Der große Vorteil eines 2D-Systems gegenüber seinem „großen Bruder“ ist im Wesentlichen die Tatsache, dass ein 2D-System inline-fähig ist, also eine Automatisierte Röntgeninspektion (AXI) erlaubt. Die Qualität einer Lötverbindung lässt sich mit einem 3D-Röntgensystem wesentlich umfangreicher und besser beurteilen. Auch spielt es keine Rolle, ob die Leiterplatte ein- oder zweiseitig bestückt ist. Das alles hat natürlich seinen Preis, und wo ein 2D-System von den Anschaffungskosten bereits einen Spitzenplatz unter den Testsystemen belegt, ist ein 3D-System hierbei der absolute Überflieger.

Weitere Alternativen zur optischen Kontrolle der „unsichtbaren“ Lötverbindungen sind leider nicht in Sicht und so muss man, möchte man auf diesen Punkt auch bei den neuen Bauformen nicht verzichten, wohl oder übel diese bittere Pille schlucken oder sich gänzlich neu orientieren.

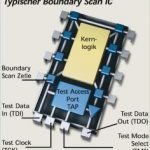

Sehr viel einfacher löst ein Testverfahren die Problematik der mechanischen Adaption der Leiterbahnen für die elektrische Überprüfung der Baugruppe – JTAG/Boundary Scan. Sehr frühzeitig hat die „Joint Test Action Group (JTAG)“ die Herausforderungen, die an das elektrische Testen künftig gestellt werden, erkannt und standardisiert: IEEE 1149.x. Der Standard beschreibt die Struktur für einen Zugriff auf die Leiterbahnen einer Baugruppe mittels in den Bauteilen selbst integrierter zusätzlicher Logik, den Boundary-Scan-Zellen. Die Kommunikation mit den Boundary-Scan-Zellen erfolgt dabei über einen vierdrahtigen Testbus. Ein solches Boundary-Scan-fähiges Bauteil ist schematisch in Bild 4 dargestellt.

Boundary Scan bietet die Möglichkeit zur elektrischen Adaption der Leiterbahnen. Man kann fast schon von einem uneingeschränkten Zugriff schwärmen, da sämtliche Nachteile der mechanische Adaption, besonders die, welche das Setzen der Testpunkte betrifft, verschwinden. Wirklich? Ob eine Baugruppe mittels Boundary Scan mit einer zufrieden stellenden Abdeckung getestet werden kann, entscheidet sich in der Entwicklung. Denn Boundary Scan setzt voraus, dass mindestens ein Boundary-Scan-fähiger Baustein auf der Baugruppe zu finden ist und man dessen Testbus auch verdrahtet hat. Boundary Scan beschränkt sich zur Zeit vornehmlich auf den digitalen Bereich. Das analoge Testen ist zwar in dem Standard IEEE 1149.4 beschrieben, doch ist die Anzahl verfügbarer Bauteile mit diesem Standard noch begrenzt.

Noch eine Anmerkung zu den Kosten eines Boundary Scan Testsystems: Denkt man kurz darüber nach und führt sich vor Augen, dass der Boundary-Scan-fähige Baustein seine Messtechnik quasi selbst mitbringt, so wird man zwangsläufig in diese kostengünstige Richtung tendieren. Derzeit stellt Boundary Scan das mit Abstand wirtschaftlichste Testverfahren dar. Demnach dürfte klar sein, dass Boundary Scan in der Teststrategie von morgen nicht fehlen darf.

EPP 463

Unsere Webinar-Empfehlung

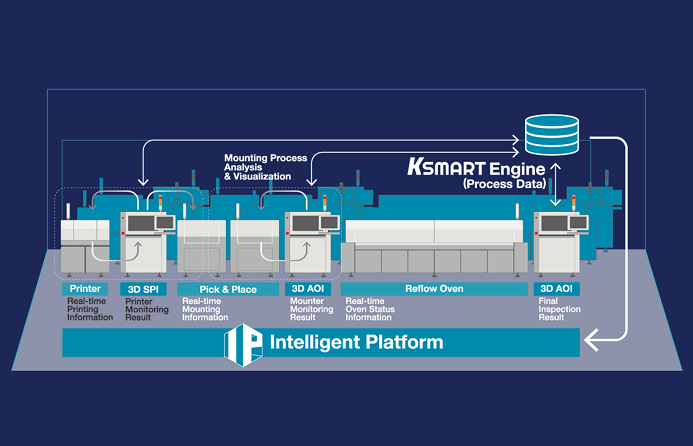

Die Nutzung der 3D-Mess- und Prozessdaten bringt die Produktionssteuerung auf die nächste Stufe. Echte 3D-Messung ermöglicht KI-basierte Prozessmodellierung zur Vorhersage von Parameteränderungen und -defekten oder zur Ursachenanalyse bis hin zu einzelnen Werkzeugen und Best…

Teilen: