Mit immer weiteren „Klimmzügen“ versucht die Elektronikindustrie Anforderungen wie kleinere Abmessungen, geringeres Gewicht, niedriger Stromverbrauch, höherer Funktionsumfang, Zuverlässigkeit und Umweltverträglichkeit unter einen Hut zu bekommen. Dabei ist der Druck durch kürzere Innovationszyklen und hohem Qualitäts-und Kostendruck erheblich. Mit neuen Gehäuse- bzw. Aufbaubautechniken (Advanced-Packages) kann man einige Probleme lösen, beispielsweise mit MCMs auf Si-Substrat.

Hans-Wolfgang Diesing,Strand Interconnect

Die Baugruppenherstellung folgt der Entwicklung durch die Anwendung immer kleineren Bauelemente von SMD über CSP bis zu Chip-on-Board (COB), Ball-Grid-Array (BGA) oder Flip-Chip. Die überproportional zunehmende Anschluß- und Verdrahtungsdichte zwingt dabei zu aufwendigen und zeitraubenden Verbindungstechniken wie Laserdrilling oder Wirebonding, die bei fortschreitender Minimierung der Dimensionen sowie gestapelten Verbindungsebenen zu gravierenden Ausbeute- und Zuverlässigkeits-Problemen führen. Dem tritt die Halbleiterindustrie entgegen, indem sie versucht, immer mehr Funktionen in einen Chipzu integrieren (System-in-a-Package, Systems-on-a-Chip usw.), und damit der Anschluß- und Verdrahtungsdichte auf der Platine zu entlasten.

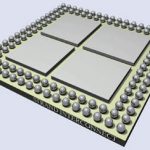

In Systems-on-a-Chip kombiniert man digitale Funktionen mit Analogschaltungen und verschiedenen Speichertechniken auf einem Die (Chip). Dies gelingt nur mit erheblichen Ausbeute-Verlusten, zumal die verschiedenen, kombinierten Technolo-gien unterschiedlichen Ausbeutekriterien unterworfen sind, die nicht notwendigerweise gut zusammenpassen. Die Folge ist, daß viel ‚gutes‘ Silizium mit gegebenenfalls wenig ‚schlechtem‘ verworfen werden muß und damit wird die Systemintegration auf einem Chip zu teuer. Hier ist die System-on-Substrate-Integration eine sehr pragmatische Lösung, wobei ein Multilayer-Dünnfilm-Zwischenträger aus Silizium sehr positive Effekte verspricht. Insbesondere Multi-Chip-Module (MCM) auf Silizium-Substraten zeichnen sich durch kompakten Aufbau (klein, flach, leicht) sowie hohe Komplexität aus. Im Folgenden die wesentlichen Vorteil dieser Aufbautechnik:

• Performance (hohe Signalfrequenz,Taktraten und Datendurchsatz)

• Signalintegrität (geringe Leitungsver-luste, Störverhalten und Übersprechen)

• Verteilte Entkoppelung (Lagen der Bezugspotentiale dicht gekoppelt)

• Integration passiver Bauelemente (kleine Werte, hohe Toleranzen)

• Beeinflussen der Leitungsimpedanzen (Microstriplines per Design-Rules)

• Geringe Laufzeitverzögerungen (kurze Signalwege durch kleine Strukturen)

• Gute EMV (enge Kopplung an Bezugspotential)

• Hohe Zuverlässigkeit (angepaßte Wärmeausdehnung, gute Wärmeleitung)

• Erweiterter Temperaturbereich (Prozeß bis 350 °C)

• Umweltverträglichkeit (halogenfreie Herstellung, bleifrei

• Verbesserter Nachbauschutz (gegen-über Bestückung mit herkömmlichen ICs)

• Schnelle Markteinführung (Dünnfilm-Lithografie in Entwicklung und Produktion)

• Geringe Kosten (kurzer Vorlauf, niedrige Investitionen, hohe Ausbeute)

Diese Vorteile beziehen sich auf eine zwar nicht brandneue aber erst kürzlich durch Strand Interconnect für einen breiten Markt nutzbar gemachte Technik von Dünnfilm-Fotovia-Substraten auf Silizium-Wafern für Multi-Chip-Module. Die Fertigung ist weitgehend automatisiert. Jährlich können 60.000 Wafer mit 200-mm-Durchmesser und 4 Metallisierungslagen gefertigt werden, jeder Wafer enthält durchschnittlich einige hundert Substrate. Damit lassen sich kostengünstig Millionen von hochdichten Interconnect-Substraten fertigen. Diese Kapazität kann bei Bedarf noch verdreifacht werden.

Die und Substrataus gleichem Material

Die Substrate können auf verschiedene Arten weiterverarbeitet werden: mehrere Chips lassen sich perWirebond oder als Flip-Chips auf dem Silizium mit der Dünnfilm-Mehrlagen-Verdrahtung unterbringen. Dieses Multi-Chip-Substrat kann nun selbst wie ein Chip verkapselt werden oder in Chip-on-Board-Manier direkt auf einer Platine, einem Kühlkörper oder Keramik-Träger montiert werden, um dann per Wirebond mit den Laminatverbindungen oder Dickfilm-Leiterbahnen bzw. auchdirekt mit Steckverbinderpfosten zur Außenwelt kontaktiert zu werden. Die bausteininterne, hohe Anschlußdichte zwischen den Chips wird auf vergleichsweise wenige elektrische Anschlüsse nach außen reduziert. Auf dem Substrat entstehen keine Ausdehnungsspannungen durch Temperaturzyklen, weil die Wärmeausdehnung zwischen Chip und Substrat perfekt angepaßt ist – schließlich bestehen beide aus demselben Material (Silizium). Die Wärmeleitfähigkeit von Silizium steht der von Aluminium kaum nach und ist damit deutlich besser als Keramik oder Laminat. Damit können Hot-Spot-Effekte (lokale Überhitzung durch Power-Chips) vermieden werden. Durch gute Wärmeverteilung läßt sich eventuell auch die Zwangskühlung einsparen oder reduzieren.

Die Siliziumwafer kosten trotz perfekter Oberfläche weniger als entsprechend große Glasscheiben – schließlich hat man auch nicht die Anforderungen einer Fertigung mit Submikrometer-Diffusions-Prozessen. Wafer, die hier verworfen werden, sind noch bestens geeignet als Trägermaterial für den Dünnfilmprozeß. Als Isolierschicht wird ein aufgeschleuderter Fotolack (Benzo-Cyclo-Buthene) verwendet, der bei 200°C schnell aushärtet und danach bis 350°C prozeßfest und somit auch für die Bleifreitechnik geeignet ist. Überdies hat das Polymer eine extrem niedrige Dielektrizitätskonstante (Low K) von 2,65 und einen ausnehmend niedrigen dielektrischen Verlustfaktor von 0,0008. Die besonders gute Resistenz gegen Feuchte qualifiziert das Material auch als Schutzschicht gegen Umwelteinflüsse.

Die Dimensionen des Schichtaufbaus liegen im Mikrometerbereich: die Isolierschicht ist 3 bis 7 µm dick und die darauf gesputterte Aluminium-Metallisierung hat 2 bis 3 µm. Bis zu vier isolierte Aluminiumlagen können so aufgebaut und perFoto-Vias durchkontaktiert werden. Die Leiterbahnen haben ein Flächenraster von 45 µm (etwa Haaresbreite). Die Verdrahtungsdichte steht der auf Chips kaum nach und kann zumindest partiell ein Vielfaches an Lagenzahlen auf einer Multilayer-Leiterplatte erreichen und damit erhebliche Kosten einsparen.

Aufbauohne Verkapselung

Derzeit wird ein weiteres Verbindungskonzept entwickelt, das eine Bestückung des Multi-Chip-Substrats ohne Verkapselung erlaubt (Direct-Attach-Substrate). Die Idee dahinter baut auf den guten Versiegelungseigenschaften der Isolations-Schicht auf und dem Umstand, daß Flip-Chips mit kleinen Anschlußrastern nicht voll den großen Ausdehnungskräften eines im Temperatur-Ausdehnungskoeffizienten abweichenden Basismaterials ausgesetzt sind. Kritisch ist nur noch die gröbere Verbindung zur Leiterplatte. Sie sind durch Lotkugeln vorgenommen, deren Durchmesser die Dicke der abgedünnten Flip-Chips überragt. Andere Verbindungstechniken mit Leitklebern, Elastomeren und Gold-Bond-Stümpfen bieten hier möglicherweise bessere Chancen auf eine zuverlässige Verbindung, die auch bei größerer Ausdehnung und einer höheren Zahl von Temperaturzyklen dauerhaft belastbar ist.

Die Einsatzgebiete für die Multichip-Integration sind vielfältig und umfassen alle Berei-che von Elektro-nikschaltungen in praktisch allen Geräten, speziell auch dort, wo etwas Leistung umgesetzt wird. Für diese Anwendungsfelder wie Motorsteuerungen, Lichtsteuerungen, getaktete Netzteile und Power-Management-Systeme können Multi-Chip-Silizium-Substrate schon wegen der guten Wärmeableitung, minimierten Störstrahlung und des extremen Minimierungspotentials bei hoher Zuverlässigkeit interessant werden. Zudem handelt es sich hierbei um Einheiten, für die in einem integrierten Modul keine eigene Kapselung nötig ist und dadurch nicht nur Platz sondern auch Kosten sparen. Für erhöhte Betriebstemperaturen zwischen 150 und 180 °C kann eine Betriebsdauer von 30 bis 50 Jahren extrapoliert werden.

HoheAusbeute inklusive

Wesentliche Aspekte bei dieser Form der Baugruppen-Miniaturisierung sind neben Performance und Zuverlässigkeit die hohe Ausbeute von nahezu 100 % nach Assemblierung und Verkapselung, an die auch orga-nische Multichip-Substrate bisher kaum heranreichen. Das ist um so wichtiger, weil hier getestete Chips verwendet werden und deshalb substantielle Verluste in der Ausbeute die Kostenkalkulation auf Systemebene empfindlich treffen. Selbst etablierte globale Assembly- und Packaging-Dienstleister tun sich hier schwer, in der Gesamtkalkulation mitzuhalten auch wenn organische Substrate grundsätzlich kostengünstiger an-geboten werden. Vom universitätsnahen IMC-Institut wurde 1997 die Firma Strand Interconnect gegründet mit der Geschäftsidee, 5-Zoll-Waferdünnfilmfertigung auf 8 Zoll zu portieren. 1998 ging man mit dem Businessplan an die schwedische Innovations-Börse und konnte sich mit dem nötigen Kapital ausstatten für den Aufbau einer automatisierten Dünnfilm-Waferfab. Derzeit werden einige Millionen Substrate gefertigt. Die Investitions- und Wartungskosten liegen um mindestens eine Größenordnung niedriger als bei einer Waferfabrikation mit Submikrometer-Diffusions-Prozessen. Die Fertigung kann mit zwei Mann Bedienungspersonal aufrecht erhalten werden. Das übrige Personal für Management, Marketing, Akquisition, Administration und Entwicklung zählt nur weitere elf Angestellte. Durch die vergleichsweise geringen Investitionen und Betriebskosten sowie die schlanke und flache Personalstruktur können die Kosten insgesamt auf niedrigem Niveau gehalten werden. Sobald die Auslastung der momentanen Fertigungsressourcen erreicht ist, bestehen Pläne, die Reinraumfläche zu verdoppeln.

EPP 258

Unsere Webinar-Empfehlung

Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine zeitnahe schnelle Messung…

Teilen:

.png)