Während die Welt über den „nickel tag“ diskutiert – ein passives RFID-Label zum Preis von 5 US-Cent – und ob es ab 2008 am Markt sein kann, folgen die Anbieter von Backend-Equipment aggressiv diversen Technologiepfaden, um die Fertigungskosten für universell einsetzbare RFID-Tags drastisch zu reduzieren.

Hugo Pristauz, Datacon, Radfeld (Österreich)

Die Einsatzmöglichkeiten, welche die RFID-Technologie bietet, sind unvorstellbar, und Analysten stellen dar, dass die breite Anwendung von RFID in zwei Phasen erfolgen wird: In Phase 1, in der wir uns gerade befinden und in der nur marginale Fortschritte erzielt werden, wird RFID in bestehenden Geschäftsprozessen eingesetzt. Die revolutionären Veränderungen finden in Phase 2 statt, wenn sich durch ein radikales Reengineering der Geschäftsprozesse ein RFID-zentriertes Business entwickelt, wodurch das in dieser Technologie schlummernde Potenzial zum Tragen kommen wird. Es ist zu kritisieren, dass sich die Welt viel zu beharrlich auf das Fallen der Preise von RFID-Tags konzentriert, anstatt mit der nötigen Kreativität an die Umsetzung radikaler Schritte heranzugehen.

Der Preis eines RFID-Tags ist derzeit der wesentliche Benchmark für die Akzeptanz dieser Technologie im breiten Markt. Man spricht vom so genannten „nickel tag“, einem voll funktionsfähiger passiven RFID-Transponder-Tag, der im Jahr 2008 für einen Nickel (5 US-Cent) erstanden werden kann. Während der Durchschnittspreis eines RFID-Tags im Jahre 2003 noch beim 10fachen Wert lag, ist es auffällig, dass auf breiter Front neue Technologie-Enabler in Erscheinung treten, die mithelfen, die Produktionskosten von RFID-Tags unter 5 Cent zu treiben

Grundlegende Technologien für RFID-Chipmontage

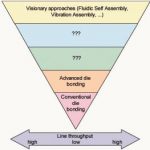

Die Verfahren zur Chipmontage auf einem Substrat sind über Dekaden hinweg entwickelt und optimiert worden; sie sind als konventionelle Die-Bonding-Technologie bekannt. Auf der Basis dieses Know-hows werden von den Equipment-Firmen nun hoch entwickelte Die-Bonder für High-Speed Flip-Chip-Assembly angeboten. Wegen des hohen antizipierten Volumenbedarfs an RFID-Tags sind in letzter Zeit etliche alternative Verfahren (z.B. fluidic self-assembly [1], vibratory assembly [7] und andere) entwickelt worden. Sie werden hier oft als „visionär“ bezeichnet (Bild 1).

Die großen Vorteile konventioneller wie hoch entwickelter Die-Bonder liegen in ihrer Technologie – mit dem Vorteil niedriger Investitionsrisiken und dem Betrieb mit hoher Ausbeute. Zur Veranschaulichung: Bei der Montage von High-end-Flip-Chip-Komponenten wie DSPs und ASICs ist eine Fertigungsausbeute von > 99,95% eine Standardvorgabe. Bei Low-end-Flip-Chip-Komponenten, wie es die RFID-Tags sind, rechnet man mit einer Standard-Ausbeute von 98%. Eine Optimierung auf 99% ist realistisch, wenn alle Prozess- und Materialparameter gut kontrolliert werden. In mittelfristiger Sicht sollten 99,5% erreichbar sein.

Zum besseren Verständnis der Kosten-Pareto-Kurve des Ausbeuteverlusts sei hier ein einfaches Rechenbeispiel dargestellt: Eine komplette Chipmontage-Linie einschließlich Kleber-Auftrag, Flip-Chip-Montage, Aushärten, Test und Slitting ist derzeit zu einem Marktpreis von < 1 Mio. US-Dollar erhältlich. Bei 7400 produktiven Stunden im Jahr, einem Liniendurchsatz von 10.000 UPH und fünf Jahren Abschreibungszeitraum liegen die Kosten der Chipmontage bei 0,27 US-Cent pro RFID-Tag. Setzen wir weitere 15 US-Cent als Kosten für ein komplettes RFID-Inlay an und einen Ausbeuteverlust von 2%, dann erreichen die Kosten des Ausbeuteverlusts 0,3 Cent – was die Abschreibungskosten der Produktionslinie übersteigt. Damit sollten die großen Vorteile eines ausgereiften Produktionsverfahrens auf Basis von langjährig optimiertem Equipment klarer erkennbar sein.

Direkte und indirekte Chipmontage

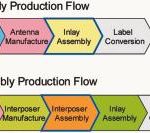

Bei der Fertigung von RFID-Inlays gibt es zwei unterschiedliche Ansätze: Direkte Chipmontage und indirekte Chipmontage (Bild 2).

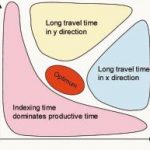

Bei der Direktmontage werden die Bumps der Chips per Flip-Chip-Technologie direkt auf die Antennenanschlüsse positioniert und mit ihnen verbunden. Als Hauptvorteil werden die insgesamt geringeren Package-Kosten angesehen, da weniger Prozessschritte und Materialeinsatz erforderlich sind. Bei hohen Durchsatzraten und großem Antennen-Pitch hat dieses Verfahren jedoch mit einem konventionellen Flip-Chip-Bonder seine Herausforderungen im Substratvorschub. Je größer der Bondbereich ist, desto weniger Einfluss haben die nicht-produktiven Zeiten des Substratvorschubes auf den Durchsatz. Der Nachteil eines großen Bondbereichs ist jedoch die längere Bewegungszeit für den Chiptransport. Nur die gut abgestimmte Dimensionierung des Bondbereiches führt zu einem erfolgreichen Maschinenkonzept (Bild 3).

Alternativ setzen einige Hersteller auf die indirekte RFID-Chipmontage. Bei diesem Ansatz wird ein Flip-Chip-Interposer eingeführt, der in einem ersten Prozessschritt mit dem Chip bestückt wird. In einem Folgenschritt wird dann der bestückte Interposer bei sehr hohem Durchsatz auf die Antenne montiert. Dies kann z.B. durch Crimpen geschehen. Die Indirekt-Montage ist speziell vorteilhaft für Hersteller, die keine Erfahrung bei der Verarbeitung von Bare-Chips mitbringen und auch nicht in das dazu nötige Know-how investieren wollen. Gleichzeitig liegen die Investitionskosten für das Montage-Equipment der fertig bestückten Interposer auf die Antennen signifikant niedriger. Nachteilig sind allerdings die höheren Package-Kosten. Auch ist die Qualität der Crimpverbindung noch immer umstritten. Deshalb werden alternative Methoden wie Löt- oder Klebverbindungen eingesetzt. Oder die Verbindung wird erst nach dem Verkleben des Interposers auf einen Karton hergestellt, und die Antenne in einem zweiten Schritt durch Überdrucken mit leitfähiger Tinte über Karton und Interposer aufgebracht.

Flip-Chip-Verbindungstechnologie und Prozessfluss

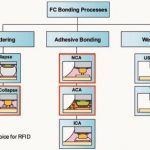

Eine weitere wichtige Wahl liegt in der einzusetzenden Verbindungstechnologie. Bild 4 zeigt die verschiedenen grundlegenden Optionen.

Als viel versprechende Technologien zur RFID-Chipmontage gelten insbesondere die Klebeverbindungen NCA (non-conductive adhesive) und ACA (anisotropic conductive adhesive) [4]. Da das vorher aufgebrachte Epoxymaterial zugleich die Funktionalität des Underfillers bietet, ist diese Verbindungstechnik sehr kostengünstig, speziell in Pastenform (NCP, ACP). Das Epoxy kann per Siebdruck oder Dispenser aufgetragen werden – wobei das Dispensieren die meisten Kosten spart, weil der Prozess mit weniger Materialeinsatz auskommt. Man beachte auch, dass NCP zu niedrigeren Kosten verfügbar ist als ACP. Deshalb erscheint NCP in dispensierter Form als die Killertechnologie zur Montage von RFID-Inlays. Vorteile von NCP sind:

- Einfache, schnelle und kostengünstige Verarbeitung

- Hochqualitative Verbindung

- Kein zusätzlicher Underfiller

- Wenige Prozessschritte

- Niedrige Epoxy-Kosten

- Hitzeverträglich mit kostengünstigen Substratmaterialien

- Nutzbar in Reel-to-Reel-Applikationen.

Die Möglichkeit hochvolumiger NCP-Verarbeitung auf Flex-Substraten wurde bereits bei der Produktion von Smart Cards demonstriert; dabei wurden nachweislich auch die Anforderungen an die hohe Zuverlässigkeit der Flip-chip-Module erfüllt [6]. Außerdem wird für die RFID-Chipmontage der nicht-kollabierende Lötprozess eingesetzt. So profitiert der GBS-Prozess (gold bump soldering) von den geringen Bumping-Kosten der Gold-Bumps und von der hohen Qualität der intermetallischen Verbindung beim Löten.

Um das Bild zu vervollständigen: Kollabierende Prozesse sind nicht sinnvoll wegen höherer Bumping-Kosten, dickerer Gehäuseprofile und der Notwendigkeit eines zusätzlichen Underfill-Schrittes – wenn man nicht einen vorher aufgebrachten Underfiller benutzt. Auch beim ICA-Prozess ist der zusätzlich notwendige Underfill-Schritt ein Nachteil. Ultrasonische (US) und thermosonische (TS) Verfahren benötigen eine mechanisch stabile Unterstützung durch das Substrat – was mit preisgünstigen Materialien wie PET bei 50 µm Dicke oder darunter nicht leicht zu erzielen ist.

Prozessfluss für Chipmontage

Die letzte Überlegung gilt dem Verständnis der verschiedenen Optionen für den Prozessfluss der Chipmontage. Der klassische Fluss, wie z.B. in der NCP-Produktion benutzt, beginnt mit der Epoxy-Applikation (per Siebdruck oder Dispenser), gefolgt vom Pick-Flip-Place (Die Attach). Das Aushärten geschieht in einem zweistufigen Prozess: der parallelen Laminierung mehrerer Chips in einer beheizten Presse (Lamination) [4] und dem finalen Aushärten in einem Inline-Ofen (Final Curing). Die Erfahrung hat gezeigt, dass sich die Zahl der Prozessschritte im klassischen Prozessfluss reduzieren lässt, indem man entweder auf den Inline-Ofen für das finale Aushärten verzichtet (Place & Laminate) oder alternativ die beheizte Presse eliminiert (Place & Cure).

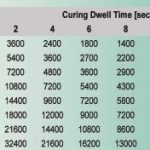

Place & Laminate wird in der Produktion von RFID-Inlays für NCP- und ACP-Packages weithin eingesetzt. Die Nachteile liegen unter gewissen Bedingungen im Durchsatz der Linie. Bild 6 zeigt den mit einer beheizten Presse erzielbaren Durchsatz, abhängig von der Zahl der Dies pro Index (die parallel zu laminieren sind) und der Aushärtezeit. Dabei wurden zwei Sekunden für die nicht-produktive Zeit während des Index sowie dem Öffnen und Schließen der beheizten Presse angenommen.

Unter der Annahme von 7500 bis 10.000 UPH für den Flip-Chip-Bonder kann – je nach Antennengröße – der Durchsatz der Linie durch die beheizte Presse entscheidend limitiert sein, speziell bei der Produktion von großen UHF-Inlays. Das ist einer der Hauptgründe, warum Montagelösungen mit Place & Cure, die bei Lötprozessen Standard sind, im Mittelpunkt künftiger Technologie-Entscheidungen stehen [2,3,4].

RFID-Tag für 5 Cent

Kommen wir zurück auf die Frage, ob ein Verkaufspreis von 5 US-Cent für ein Smart Label in den nächsten Jahren realistisch ist. Hier ein weit verbreiteter Ansatz für das Kostenbudget eines RFID-Labels:

IC-Fertigung (Wafer dünnen, bumping, dicing) < 2 Cent +

Antennenherstellung < 1 Cent +

Inlay assembly (einschl. Chip-Aattach) < 1 Cent +

Label-Konversion < 1 Cent =

Summe < 5 Cent.

Laut Meinung der Halbleiterhersteller wird die Fertigung eines RFID-ICs bei hohen Volumina für weniger als 2 Cent realistisch sein [2,5,7]. Auch die Technologien zur Antennenherstellung und Label-Konversion entwickeln sich in Richtung auf ein Kostenziel von < 1 Cent pro Stück. Es seien nun die Kosten der Inlay-Montage näher untersucht. Eine detaillierte Übersicht über alle Kombinationen technischer Lösungen für die Inlay-Montage würde hier den Rahmen sprengen. Stattdessen sei das Kostenbudget für eine spezielle schlüsselfertige Lösung einer Inlay-Montage dargestellt, die für alle zukünftigen Siegertechnologien sicher ein Benchmark sein wird:

Der Benchmark basiert auf einem UHF 4” x 1” Inlay-Montageprozess:

Allgemeine Montage-Technologie – High-Speed Flip-Chip-Bonding

Chipmontage-Methode – Direct Chip Assembly

Verbindungstechnologie – Adhesive Bonding / NCP

Prozessfluss – Place & Laminate

Epoxy-Applikation – Dispenser

Package-Test – Integriert

Slitting – Integriert

Liniendurchsatz – 10.000 UPH

Das Kostenbudget pro Inlay für den Montageprozess ist wie folgt:

Abschreibungskosten für Chip-Montage < 0,22 Cent +

Abschreibungskosten für Dispensieren < 0,02 Cent +

Abschreibungskosten für Test & Slit < 0,03 Cent +

Betriebskosten < 0,06 Cent +

Adhesive-Kosten < 0,05 Cent +

Sonstige Kosten < 0.01 Cent +

Ausbeuteverlust < 0,3 Cent =

Summe Inlay-Montage < 0,69 Cent.

Die Abschreibungskosten basieren auf einer Zeitdauer von fünf Jahren und 7400 produktiven Arbeitsstunden pro Jahr, die Betriebskosten auf einem Stundensatz von 30 Dollar einschließlich Fertigungs-Gemeinkosten. Dabei kann jeder Operator fünf Linien bedienen. Der Ausbeuteverlust bezieht sich auf 98% Ausbeute und 15 Cent Inlay-Kosten.

Als Perspektive für die nächsten zwei Jahre kann davon ausgegangen werden , dass die Equipment-Anbieter in der Lage sein werden, bei konstanten Equipment-Kosten den Durchsatz der Linien zu verdoppeln. Dabei könnte die Ausbeute auf 99,5% steigen, während die Inlay-Kosten auf unter 5 Cent fallen. Das resultiert in folgendem mittelfristigen Kostenbudget als Benchmark für die RFID-Inlay-Montage:

Abschreibungskosten für Chip-Montage < 0,11 Cent +

Abschreibungskosten für Dispensieren < 0,01 Cent +

Abschreibungskosten für Test & Slit < 0,02 Cent +

Betriebskosten < 0,03 Cent +

Adhesive-Kosten < 0,05 Cent +

Sonstige Kosten < 0.01 Cent +

Ausbeuteverlust < 0,03 Cent =

Summe Inlay-Montage < 0,26 Cent.

Schlussfolgerung

Zur kostengünstigen Fertigung von RFID-Tags ist das Verständnis der unterschiedlichen Technologien der RFID-Inlay-Herstellung essenziell. Für die Einführung neuer, visionärer Technologien sind das große Einführungsrisiko und das hohe Maß an Ausbeutekosten eine große Hemmschwelle. Zur besseren Kostentransparenz wurde ein Benchmark auf der Basis einer ausgereiften Turnkey-Produktionstechnologie präsentiert, der die Inlay-Montagekosten derzeit zu < 0,69 Cent bestimmt, wobei die Chip-Montagekosten unterhalb 0,22 Cent liegen. Zusätzlich gibt es einen Zwei-Jahres-Kostenausblick mit <0,26 Cent für die gesamte Inlay-Montage und < 0,11 Cent für die Chip-Montage

EPP 491

Referenzen:

[1] John Stephen Smith: RFID Inlay Assembly Technologies. Proceedings of the Smart Labels Conference USA, Baltimore 2005.

[2] N. J. A. van Veen: RFID Technology Development Activities at Philips. TechSearch RFID Workshop, Austin/Texas 2005.

[3] J. U. Fuhrmann, W. Reinert: FliBuSi: Flip-Chip-Bonding for ultra-thin Silicon – Verfahren zur Verarbeitung dünner Siliziumchips. Productronic 11/03.

[4] Achim Pajonk: Variable Flipchip-Montage für High Volume. Productronic 4/04.

[5] G. Swamy, S. Sarma: Manufacturing Cost Simulations for Low Cost RFID Systems. Auto-ID Center, Massachusetts 2003.

[6] P. Stampka: FCOS: Flip Chip Technology for Smart Card (contact-based) Modules. 9th European Workshop of the IEEE’s CPMT, Berlin – Feb. 2005.

[7] G. Swamy: RFID Tag Costing: Towards a 5c Tag. TechSearch RFID Workshop, Austin/Texas 2005.

Unsere Whitepaper-Empfehlung

Große Bauteile stellen große Herausforderungen an die Fokussierfähigkeit und den Höhenmessbereich der derzeit im Markt verfügbaren AOI-Systeme. Die Lösung: Innovationen, die die Vorteile von 3D-AOI nutzen, die Leistung in der Fertigung steigern und die Qualitätssicherung opt…

Teilen: