Bestandteil von DRAM- und Flash-Memory-Tests ist die Redundanzanalyse (RA) zur Ermittlung von Reparaturstellen: Damit können nach dem Wafer-Sort-Test fehlerhafte Adressen auf dafür vorgesehene redundante Speicherzellen umgeleitet werden. Aufgrund der Menge an zu verarbeitenden Testdaten setzt man bislang bei RA proprietäre Prozessore in der Testerhardware ein. Das hat Nachteile, die Verigy vermeiden kann.

Scott West, Product Manager bei Verigy, Cupertino, Kalifornien/USA

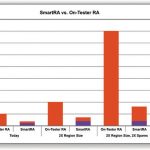

Die für RA notwendige Hardware ist nicht nur teuer und unflexibel, sondern begrenzt auch die nutzbare Lebensdauer von Wafer-Sort-Testern, da neue Speicherprodukte immer umfangreichere Analysen verlangen. Das Testsystem V6000WS mit SmartRA (Scalable Memory Redundancy Technology) verfolgt ein innovatives Konzept, um dieses Problem für aktuelle und künftige Halbleiterspeicher zu lösen. Die Verigy-Testplattform bietet eine weitaus höhere Leistungsfähigkeit und Flexibilität als bisherige Tester-RA-Architekturen. Durch die Auslagerung der RA-Berechnungen auf eine externe, dedizierte Serverfarm lassen sich komplexere Redundanzanalysen zu niedrigeren Kosten bewältigen. Zusätzlich kann die RA-Verarbeitung durch das Hinzufügen weiterer Standard-Server unabhängig vom Tester weiter skaliert werden. Dies ermöglicht eine RA-Verarbeitung heutiger Bausteine und sorgt für die notwendige Flexibilität, um den Tester auch dann kosteneffizient zu betreiben, wenn zukünftige Komponenten exponentiell umfangreichere Redundanzanalysen verlangen.

Bisherige Tester-Architekturen verwenden teure, proprietäre On-Tester RA-Prozessoren. Bei jedem Funktionaltest werden von SmartRA Fehlerdaten erfasst und auf dem Tester vorverarbeitet. Anschließend werden die erforderlichen Daten zur Blade-Serverfarm übertragen. Die Blade-Server übernehmen dann die Redundanzanalyse.

Die Übertragungszeit wächst linear mit dem Adressbereich des getesteten Bausteins. Mit steigender Zahl von redundanten Elementen allerdings erhöht sich die Anzahl potenzieller Platzierungen dieser redundanten Elemente exponentiell. Das heisst, dass die Laufzeit der RA zur RA-Komplexität des Bausteins exponentiell und zur Größe des Bausteins nur linear zunimmt.

Mit SmartRA lässt sich die Zeit für die Redundanzanalyse beträchtlich und kostengünstig verkürzen, indem man nur die Serverfarm erweitert, um so den Testanforderungen eines Bausteins gerecht zu werden. Zusätzlich zur Redundanzanalyse kann die reichhaltige und kostengünstig verfügbare Rechenleistung für mehr Analysen verwendet werden als On-Tester RA-Lösungen dies bieten können. Produkt- und Prozessingenieure erhalten somit ohne Beeinträchtigung der Testzeiten einen besseren Zugang zu Fehleranalysedaten.

Durch die Verlagerung der RA-Berechnungen von dedizierter, proprietärer Testerhardware auf Bladeserver können die Hersteller die nutzbare Lebensdauer ihrer V6000WS mit SmartRA verlängern, um auch künftige Bausteine mit höherer Komplexität, die noch intensivere Analysen verlangen, effizient testen zu können.

Nachteile der On-Tester RA-Verarbeitung

Eine kundenspezifische Hardware zur RA auf dem Tester ist teuer und verlangt den Einsatz von ASICs und FPGAs. Traditionell war diese Lösung dennoch kosteneffizient, weil die zusätzlichen Kosten, um RA ausführen zu können, für das von den Bausteindesigns verlangte RA-Processing toleriert werden konnten.

Diese Kosteneffizienz ergab sich bei Bausteinen, die optimal zum aktuellen Testerdesign passen. Im wirtschaftlichen Abschwung der vergangenen Jahre ist vielen Herstellern die fehlende Flexibilität der On-Tester RA-Verarbeitung deutlich geworden. Ohne das Geld für die Anschaffung neuer Tester bemühten sich die Hersteller, kreative Lösungen zu finden, um auf ihrem bestehenden, älteren Equipment neue Komponenten effizient zu testen. Da der Wafer-Sort-Test nicht “At-Speed” erfolgt, war die Testfrequenz der älteren Tester ausreichend. Der Pin-Count der älteren Tester begrenzt zwar den erreichbaren Site-Count, allerdings war die verfügbare Kapazität durch die Nutzung von Test-Modi und geschickten Test-Strategien sowie der schlechten Marktlage bisher mehr als ausreichend.

Für die RA bei neuen Bausteinen ist allerdings ein höherer Verarbeitungsaufwand erforderlich. Dadurch rückt die RA-Zeit in den Focus, da diese eine Entscheidung verlangt zwischen der Reduzierung des Durchsatzes, um eine vollständige RA durchführen zu können, und dem Abbrechen der RA bereits im Anfangsstadium. In letzterem Fall muss wegen des Fehlens einer optimalen RA-Lösung, eine geringere Ausbeute in Kauf genommen werden. Daher wird die On-Tester-RA zur Begrenzung der Testeffizienz.

Die Kapazitäten und Geschwindigkeiten von Speicherbausteinen wachsen weiter. Gleichzeitig steigt auch die Komplexität der RA für diese Bausteine. Durch die weitere wirtschaftliche Erholung der Branche und der damit einhergehenden Ausschöpfung vorhandener Testkapazitäten, können ältere Tester nicht mehr länger kosteneffizient arbeiten.

Überblick Redundanzanalyse

Die Einnahmen pro Wafer lassen sich nicht maximieren, indem man die perfekten Speicherbausteine herstellt. Viel mehr moduliert der Gewinn pro Wafer mit der Fähigkeit Bausteine herzustellen, die die Reparatur von Fehlern ermöglichen, die statistisch signifikant auftreten.

Während des Tests gefundene Fehler im Memory-Array werden repariert, indem man Sicherungen (Fuses) durchtrennt und dadurch schlechte Adressen auf redundante oder als Ersatz vorhandene Bereiche im Baustein umleitet. Der Nutzer des Speichers, ja selbst der Memory-Controller bemerkt von diesen Reparaturen nichts. Die Mehrzahl der genutzten Speicherbausteine haben ein paar Fehler, die repariert wurden.

Doch wieviel Redundanz sollte ein Memory Baustein haben? Dies hängt von der erwarteten Zahl von Fehlern im Fertigungsprozess ab. Durch mehr Redundanz im Baustein steigt zwar einerseits die Ausbeute, andererseits vergrößern sich jedoch die Die-Abmessungen. Dies führt zu weniger Dies pro Wafer. Speicherhersteller optimieren die Menge redundanter Zellen, um ihren Umsatz pro Wafer zu maximieren. Dabei muss ein Kompromiss zwischen Ausbeute und Dies pro Wafer gefunden werden. Ein typisches DRAM enthält etwa 5 bis 10 Prozent Redundanz. Ein typischer Flash-Baustein hat weniger Redundanz und erfordert einen geringeren RA-Aufwand. Zur Reparatur von Bausteinen kann die Redundanzanalyse nach dem ausführen aller Wafer-Sort-Tests auf dem Tester berechnet werden. Ein einziger Durchlauf der RA, möglicherweise während der Wafer gewechselt wird, stellt keine großen Anforderungen an die Tester-RA-Verarbeitung. Doch der Wert in der RA besteht nicht nur in der Bausteinreparatur. Während eines Wafer-Sort-Testablaufs werden dutzende Tests nach verschiedenen Algorithmen ausgeführt. Jeder dieser Tests liefert auf einzigartige Weise nützliche Daten über die getesteten Bausteine und den Fertigungsprozess.

Zur Optimierung des Testablaufs möchten Testingenieure wissen, welche Test-Algorithmen neue Fehler finden und welche nicht. Von besonderem Interesse sind Fehler, die eine Anpassung der Reparaturlösung erfordern. Einfach nur die Zahl der Fehler zu betrachten kann irreführend sein. Zum Beispiel kann ein Defekt, der eine ganze Zeile (Row) „schwächt“, zufällige Bitfehler auf dieser Zeile hervorrufen. Ein zweiter Test (oder der gleiche Test noch einmal ausgeführt) wird zusätzliche Fehler auf der Zeile finden, jedoch keinen zusätzlichen Defekt oder eine zusätzliche Reparaturlösung.

Prozessingenieure möchten wissen, welche Tests welche Fehler gefunden hatten, um daraus den Fehlertyp abzuleiten und den „Root-Cause“ des Problems im Produktionsprozess zu finden. Einfache Fehlermuster in einem Speicher, darunter Single-Bit-, Double-Bit-, Single-Row- und Double-Row-Fehlermuster, sind so nützlich, dass DRAMs bei der Herstellung anderer Halbleiter jahrzehntelang als Prozessüberwachungsbausteine verwendet wurden.

Obwohl die Redundanzanalyse idealerweise nach jedem Funktionaltest durchgeführt werden sollte, werden in der Praxis Kompromisse geschlossen.

Faktoren und Trends bei Anforderungen für die RA

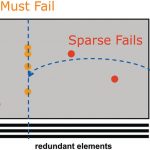

Die richtige RA-Lösung zu finden, verlangt zwei grundsätzliche Schritte: Must Repair (MR) Analyse und Sparse Repair Analyse. Die MR-Analyse ermittelt, wo spezielle redundante Elemente verwendet werden müssen. Falls zum Beispiel eine Memory-Region drei redundante Spalten (Columns) hat, muss jede Zeile mit vier oder mehr fehlerhaften Adressen mit einer redundanten Zeile repariert werden. Die Must Repair Analyse ist iterativ. Falls eine der drei redundanten Spalten in der MR-Analyse verwendet wird, reduziert sich die Grenze für Row-MR auf zwei. „Must Repairs” sind leicht zu finden und erfordern nur relativ einfache RA-Berechnungen.

Die Fehler, die nach der MR noch vorhanden sind, sind die Sparse-Fehler. Die Sparse-Analyse ist der Teil der RA-Verarbeitung, welcher i.a. den Großteil des Berechnungsaufwands erfordert. In Fällen, bei denen nur wenige Fehler auftreten und nur wenige redundante Elemente zu berücksichtigen sind, ist die Sparse-Analyse sehr schnell. In einigen Fällen kann die Anzahl der Fehler in einer Region verwendet werden, um festzustellen, dass ein Baustein nicht reparierbar ist. Die Sparse-Analyse kann in diesem Fall entfallen. Es sind die Fälle, die nicht eindeutig irreparabel sind, bei denen aber viele Kombinationen redundanter Elemente berücksichtigt werden müssen, welche den größten RA-Verarbeitungsaufwand verlangen. Bei steigender Zahl verfügbarer redundanter Elemente erhöht sich die Zahl möglicher Kombinationen, die analysiert werden müssen, geometrisch.

Im allgemeinen gibt es verschiedene valide Reparaturlösungen für einen Baustein, die jedoch nicht gleichwertig sind. Einige Lösungen bringen bei der Bausteinreparatur mehr Risiken mit sich oder verursachen längere Laufzeitverzögerungen im Speicher. Zum Beispiel könnte es vorteilhaft sein, eine Spalte statt eine Zeile zu verwenden, um einen Single-Bit-Fehler zu reparieren. Allerdings ist es wiederum vorteilhafter, nur eine Zeile statt zweier Spalten zur Fehlerbehebung zu verwenden. Mit einer vollstandigen RA kann alle möglichen Lösungen verglichen und eine Lösung mit dem geringsten Risiko gefunden werden.

Die Faktoren, die den Umfang der erforderlichen RA bestimmen, werden durch Fehlerraten und Muster bestimmt, die sich während des Tests ergeben. Auch das Baustein-RA-Design sowie die Strategie zur verwendeten Fehleranalyse wirken sich auf den Umfang der erforderlichen Redundanzanalyse aus.

Höhere Fehlerraten, die speziell beim Anlaufen der Produktion neuer Bauteile oder bei einem neuen Prozess entstehen, erfordern einen höheren RA-Umfang. Die exakte Beziehung ist jedoch nicht trivial. Ein Anstieg bei den Must Fails reduziert die Komplexität, während zu viele Fehler offensichtlich die Reparatur eines Bausteins verhindern. In diesem Fall kann die Analyse komplett entfallen.

Im Design neuer Bausteine erhöhen sich weiter die Anzahl redundanter Elemente, sowie auch die Einschränkungen, wie diese verwendet werden können. Mehr redundante Elemente erhöhen die Zahl möglicher Lösungen, reduzieren die Anzahl von Must Fails (höheres MR-Limit) und erhöhen die Wahrscheinlichkeit, dass die Analyse durch Fehler an den „Spares“ selbst komplexer wird.

Bei der Suche nach RA-Lösungen sind für die Analyse auch Teststrategien zu berücksichtigen. Zum Beispiel ist ein parziell reparierter Die nicht wertlos, denn er kann möglicherweise als Baustein mit geringerer Speicherkapazität genutzt oder in einer Applikation verwendet werden, die einige wenige Fehler toleriert. Flash-Bausteine nutzen häufig Error Correction Codes (ECC). Damit kann ein als “gut” gelabelter Baustein ein paar Fehler pro Zeile aufweisen. Aus diesem Grund müssen mehr mögliche, gültige Lösungen miteinander verglichen werden. Test- und Prozessingenieure können Best Solution Daten verwenden, selbst wenn die Lösung den Baustein nicht vollständig repariert.

Bei neuen Speicherbausteinen erhöhen sich die Kapazitäten, Frequenzen und RA-Komplexitäten ständig. Beim Wafer Sort, wo die Redundanzanalyse erfolgt, steigen sowohl die Bausteingröße wie auch die Zahl der parallel getesteten Dies. Und obwohl der Test nicht bei der vollen Betriebsgeschwindigkeit des Bausteins ausgeführt wird, geht der Trend dahin, die Testfrequenz zu erhöhen, um die Testzeit zu verkürzen und den Durchsatz zu steigern. Eine kürzere Testzeit lässt jedoch weniger Zeit für die Redundanzanalyse. Diese Anforderungen machen ein skalierbares RA-Konzept unumgänglich.

epp477

Unsere Webinar-Empfehlung

10.10.22 | 10:00 Uhr | Conformal Coating ist ein wichtiges Verfahren, um elektronische Baugruppen vor dem vorzeitigen Ausfall zu schützen. Damit bekommt der Beschichtungsprozess eine immer höhere Bedeutung. Dabei ist die Auftragsstärke ein wichtiges Qualitätskriterium. Nur eine…

Teilen: