Die meisten Elektronikhersteller kennen die Probleme: Der weltweite Wettbewerb drückt die Preise nach unten, gleichzeitig nimmt der Funktionsumfang und die Möglichkeiten der Produkte zu. Zudem werden die Produktzyklen immer kürzer. Durch die geringeren Gewinnspannen müssen die Produktkosten soweit als möglich reduziert werden. Diese beinhalten die Testkosten, die normalerweise aber mit zunehmender Produktkomplexität steigen.

Andrew Armutat, Keithley Instruments, Cleveland (USA)

Für die Test- und Produktionsingenieure ist diese Entwicklung eine entscheidende Herausforderung. Die Integration von analogen, digitalen und sogar HF-Schaltungsteilen auf einem einzigen SOC (System-on-Chip) bedeutet bei jeder neuen Bauteilgeneration mehr Schaltungen auf weniger Platz sowie höhere Pinzahlen. Ein ähnlicher Trend ist bei diskreten Bauteilen feststellbar, wo durch die Konsolidierung von mehreren Komponenten auf einem einzigen Chip ebenfalls eine höhere Dichte und kleinere Bauformen erreicht werden. Höhere Pinzahlen erfordern mehr Testkanäle um einen akzeptablen Durchsatz gewährleisten zu können, während die Testsystemdichte wegen des beschränkten Platzes in der Produktion ebenfalls erhöht werden muss. Diese Faktoren erreichen mittlerweile die Grenzen der Testtechnologie.

Allerdings kann die heute oft praktizierte Konzentration von Funktionstests in der Endfertigung zu hohen Verlusten führen, da fehlerhafte Produkte bereits viele Prozessschritte durchlaufen haben, und die hierdurch verursachten Produktionskosten somit verloren sind. Damit ist ein Umdenken, hin zu einem möglichst frühzeitigen Test, erforderlich, um fehlerhafte Teile früher im Produktionsprozess herausfiltern zu können. Leider stellen die großen Funktionstestsysteme für den Endtest im Allgemeinen keine effizienten Lösungen dar, um Komponenten und Module in den früheren Produktionsschritten zu testen.

Die gegenwärtig in der Produktion eingesetzten ATE-Systeme lassen sich entweder als sperrige, teure Mainframe-basierende Systeme, langsame Instrumenten-basierende Systeme mit PC-Steuerung oder schnelle Instrumenten-basierende Systeme, die äußerst komplex zu entwickeln sind, kategorisieren. Keine dieser Lösungen ist für Frontend- und Backend-Prozesse optimiert. Um konkurrenzfähige Preise erreichen zu können, benötigen die Hersteller Testverfahren, Instrumente und Systeme, die ihnen eine Minimierung der Test- und Betriebskosten erlauben. In vielen Fällen wird nach Möglichkeiten gesucht, die Betriebskosten durch eine Verbesserung der Leistungsfähigkeit der bestehenden Testlösungen zu minimieren, so dass diese mehr Testlast übernehmen können. Dadurch lassen sich die hohen Kosten durch die Tests am Ende der Fertigungslinie reduzieren. Kurz gesagt gehören zu den wichtigsten Forderungen an Testsysteme:

- Erhöhung des Durchsatzes (kürzere Testzeiten).

- Minimierung der Grundfläche des Testsystems und des notwendigen Platzes im Rack.

- Reduzierung der Entwicklungszeit.

- Niedrigere Folgekosten.

Testsystem-Architektur an Anwendung angepasst

Um sich diesen Herausforderungen stellen zu können, müssen die Produktionstestingenieure im ATE-Markt nach neuen Hardware- und Softwarestrukturen suchen, welche den besten Nutzen bei den benötigten Testfunktionen (d.h. bestes Preis/Leistungsverhältnis) bieten. Welches die kostengünstigste Anlage ist, hängt natürlich von den Anforderungen der jeweiligen Anwendungen ab. In den meisten Fertigungsumgebungen werden normalerweise eine Reihe von sich ständig wiederholenden Komponenten- oder Modul-Testfolgen benötigt, die eine Spannung oder einen Strom einspeisen, die DUT-Reaktion (Device under Test) messen, diese mit vorgegebenen Grenzwerten vergleichen und dann eine Pass/Fail-Entscheidung treffen. Dies gilt besonders für die Prozessschritte am Anfang des Produktionsprozesses. Natürlich sind für diese Anwendungen genaue Quellen- und Messfunktionen mit geringem Störpegel obligatorisch.

Einfache zwei- bis vierpolige Bauteile: In diese DUT-Kategorie gehören Dinge wie Schaltungsschutzbauteile, Dioden, LEDs, Transistoren, lineare Regler, DC-DC-Konverter, Optokoppler, MEMS-Schalter (Mikroelektromechanische Systeme) und Relais. Für zweipolige Bauteile lässt sich eine relativ einfache Source-Measure-Prozedur nutzen. Drei- und vierpolige Bauteile erfordern komplexere Tests und zwei schnelle Testkanäle, um genaue I-V-Kennlinien aufnehmen zu können. Bei den neusten Bauteilhandlern, die Geschwindigkeiten von 10 ms pro Bauteil erreichen, kann allerdings die Geschwindigkeit der im Testsystem eingesetzten Instrumente zum Engpass werden.

Bauteil-Arrays: Hierzu gehören Widerstands-Arrays, TVS-Arrays (Transient Voltage Suppression – Überspannungsbegrenzung), integrierte Ferritperlen und Flip-Chip-Arrays. Bei diesen Bauteilen werden dieselben Tests wie bei den diskreten Varianten dieser Komponenten ausgeführt. Allerdings müssen alle Einzelbauteile des Arrays den Test ohne Fehler durchlaufen, damit das ganze Array als fehlerfrei gilt. Um einen hohen Durchsatz zu erreichen, ist für die Array-Produktion ein paralleler Test mit mehreren Testkanälen erforderlich.

Test von ICs/RFICs/Bauteilen auf dem Wafer: Diese Kategorie umfasst eine große Auswahl komplexer Bauteile. Am Anfang des Produktionsprozesses erfolgen normalerweise Ruhestrom- und Leckstrommessungen im Nanoampere-Bereich. Diese hohe Empfindlichkeit ist auf Grund des Low-Power-Designs erforderlich, das eine lange Batterielaufzeit ermöglichen soll. Außerdem umfasst dieser Test normalerweise einige einfache DC-Messungen, um die grundlegende Funktionalität aller Bauteile auf dem Wafer zu überprüfen. Da Tausende von Bauteilen auf dem Wafer vorhanden sind, ist ein schneller mehrkanaliger Test ein Muss.

Andere komplexe Bauteile/Module: Hierzu gehören beispielsweise Stromversorgungen, Datenerfassungskarten, RFIC-Leistungsverstärker und hybride ICs. Diese Tests erfordern unterschiedlichste Instrumente und Messungen, die von DC bis HF reichen können. Es ist oftmals ein straffes Timing zwischen den Source-Measure-Sequenzen und den verschiedenen Instrumenten notwendig, um eine genaue Charakterisierung der DUTs ermöglichen zu können. Für den Aufbau kundenspezifischer Systeme mit vielen parallelen Kanälen werden normalerweise skalierbare Instrumente und Testsystemmodule benötigt.

Testsystemarchitekturen

Bei der Auswahl einer Testlösung für die Produktion stehen die drei bereits erwähnten Kategorien zur Verfügung:

- Eigenständige/einkanalige I-V-Lösungen

- Parallele I-V-Testsysteme

- Skalierbare mehrkanalige Systeme.

Eigenständige/einkanalige I-V-Lösungen sind oftmals in weniger kostensensitiven Anwendungen einsetzbar, wo die geringere Geschwindigkeit einer sequenziellen Source-Measure-Prozedur ausreicht. Durch den Einsatz mehrerer Source-Measure-Units (SMUs) sowie mit oder ohne Schaltermatrix lassen sich mehrkanalige Systeme realisieren, die allerdings eine begrenzte Rack-Dichte und einen eingeschränkten Durchsatz aufweisen. In kleineren Systemen werden die SMUs normalerweise mittels eines PCs über GPIB und/oder externe Triggerleitungen gesteuert. Manche Lösungen verfügen über einen internen Programmspeicher, mit dem sich Testfolgen speichern, und ohne die PC-Steuerung ausführen lassen, was die ansonsten relativ langsame Kommunikation über GPIB etwas beschleunigt. Häufig werden Testanwendungen für PC-Steuerrechner unter Verwendung von SCPI-Befehlen entwickelt, die besonders dann unverzichtbar sind, wenn die SMU nur über eingeschränkte oder keine Möglichkeiten zur Programmspeicherung verfügt.

Parallele I-V-Systeme werden für den gleichzeitigen Test mehrerer DUTs oder für einen Test mit mehreren Kanälen bei komplexeren Bauteilen eingesetzt. Je nach DUT kann die Geschwindigkeit durch das Instrument, das Anwendungsprogramm oder durch die Einschwingzeit des DUTs (zu frühe Messungen führen zu ungenauen Ergebnissen) begrenzt werden. Zu den weiteren Einschränkungen bei aktuellen parallelen Testsystemen gehören sequenzielle Kanäle, im Gegensatz zu simultanen Source-Measure-Möglichkeiten, eingeschränkte Spannungs- oder Strombereiche, eine zu geringe Flexibilität sowie zu große oder zu teure Systeme (wegen einer unangemessen hohen Empfindlichkeit der eingesetzten Instrumente oder wegen Designs, die von Grund auf für bestimmte Anwendungen entwickelt wurden).

Skalierbare Systeme, im Gegensatz zu den anderen beiden Architekturen, beinhalten diese oftmals unterschiedlichste Instrumente für den Test komplexer Bauteile. Zu den beiden häufigsten Typen von skalierbaren mehrkanaligen Systemen gehören (a) integrierte Funktionstester und (b) I-V-Testsysteme auf der Basis von Open-API-Instrumenten (Application Program Interface). „Open API“ bedeutet, dass sich kundenspezifische Testlösungen aus einzelnen Bausteinen realisieren lassen, im Gegensatz sind parametrische Tester vollständig vorgefertigte Systeme. SMUs stellen oftmals die Kernkomponenten dieser Architekturen dar, die auch andere Geräte, wie Signalgeneratoren, Oszilloskope, Spektrumanalysatoren, Schaltlösungen, etc. umfassen können.

Während SMUs in parametrischen und anderen schlüsselfertigen Testern als interne Module eingesetzt werden, sind Breitband-Instrumente meist als externen Einheiten vorhanden. In jedem Fall ist eine nahtlose Integration der Instrumente wünschenswert, um einen mehrkanaligen I-V-Test mit hoher Geschwindigkeit ermöglichen zu können. Der Vorteil von schlüsselfertigen Testern ist, dass ein Großteil der Hardware- und Software-Integration für den Anwender bereits durchgeführt wurde, während eine gewisse Flexibilität erhalten bleibt. Eine Einschränkung sind aber die relativ hohen Kosten. Im Gegensatz dazu bieten Open-API-Systeme eine hohe Flexibilität bei niedrigeren Kosten, allerdings abhängig von der Anwendung und Charakteristik der Instrumente.

Wichtige Parameter für die Reduzierung der Testkosten

Anfangs wurden fünf Systemparameter als entscheidend für eine Reduzierung der Testkosten identifiziert: kürzere Testzeiten, eine reduzierte Entwicklungsdauer, eine kleinere Grundfläche oder weniger Einbauplatz und niedrigere Folgekosten. Gewisse Aspekte dieser Parameter sollten genauer betrachtet werden.

Kürzere Testzeiten: Abgesehen von der Zeit bis die DUTs im Testadapter liegen, oder wenn von einem DUT auf das nächste DUT im Adapter umschaltet wird, lässt sich der Test in eine Reihe einzelner Zeitabschnitte aufteilen, die den größten Teil der gesamten Testzeit ausmachen. Je nach Systemaufbau gehören hierzu normalerweise:

- Einspeisezeit (beinhaltet die Einschwingzeit des Signals).

- DUT-Einschwingzeit.

- Messzeit.

- Zeiten für die Umschaltung der Messbereiche (falls vorhanden) der Source-Measure-Instrumente.

- Triggerverzögerung zwischen den einzelnen Instrumenten oder zwischen einem PC-Steuerrechner und den Instrumenten.

- Zeiten für die Datenkommunikation für Testbefehle, digitale I/O, Trigger (falls vorhanden) und die Übertragung der Daten zur Speicherung oder in den PC-Speicher.

- Programm-Ausführungszeiten, um die Messwerte mit den vorgegebenen Grenzwerten zu vergleichen und um die Pass/Fail- oder Sortier-Entscheidungen zu treffen.

- Die physikalische Bewegung des Testadapters und/oder die Zeiten für die elektrische Umschaltung.

Komplexe DUTs können die Anwendung mehrerer Stimulussignale und entsprechende Messungen erfordern, bevor der Testadapter auf das nächste Bauteil umschaltet. Die erste Verbesserungsmöglichkeit im Hinblick auf die Testzeit ergibt sich durch den Umstieg von individuellen Quellen- und Messinstrumenten auf eine integrierte SMU. Damit lassen sich die Triggerverzögerung und die Zeiten für die Datenkommunikation zwischen den einzelnen Instrumenten und dem PC-Steuerrechner reduzieren. Wenn das SMU über einen internen Programmspeicher verfügt, können die Datenkommunikations- und Latenzzeiten der Testprogramme (PC) noch weiter reduziert werden, da die SMU die Testfolge aus dem eigenen Speicher ablaufen lassen kann.

Einige SMUs haben Programmspeicher, mit dem sich bis zu 100 vordefinierte Prüfungen speichern, sowie Grenzwertvergleiche, bedingte Testprogrammverzweigungen ausführen und während der Testausführung mit oder ohne einen PC-Steuerrechner abarbeiten lassen. Mit einem derartigen Design lassen sich bei einkanaligen Systemen relativ einfach deutliche Verbesserungen bei der Testzeit erreichen. Bei Systemen mit mehreren SMUs ist dies allerdings sehr viel schwieriger, da mehrere Trigger sowie die Testablaufsteuerung koordiniert werden müssen (Kasten, Seite 54).

Wegen dieser Schwierigkeiten kann die Testablaufsteuerung eines Systems mit mehreren SMUs einfach Unterprogramme aufrufen, d.h. es werden mehrere GPIB-Befehle gespeichert, die dann über einen einzelnen SCPI-Befehl vom PC-Steuerrechner ausgeführt werden können. Damit ist aber keine Logik für die Überprüfung von Grenzwerten oder für schnelle Pass/Fail-Entscheidungen, aber auch keine DUT-Handler-Schnittstelle vorhanden. Deswegen gibt es bei diesem Design nach wie vor einen hohen GPIB-Verkehr auf dem Datenkommunikations-Bussystem. Darüber hinaus können mehrere SMUs nicht so effektiv genutzt werden, wie dies bei parallelen Testkanälen sein könnte. Stattdessen erfolgt oft ein sequenzieller Zugriff, wodurch eine marginale Verbesserung des Durchsatzes erreicht wird.

Heute verwenden schnelle SMUs einen Test-Script-Prozessor und einen schnellen Steuerbus, der einen Master-Slave-Betrieb von mehreren SMUs in einer echten parallelen Kanalkonfiguration erlaubt. Diese Art von Design wird in den System-SourceMeter-Instrumenten Modell 2601 und 2602 genutzt.

Schnelleres Scripting: Der Einsatz von Scripting und Script-Prozessoren ist nicht neu; sie werden seit langem benutzt, um Internet-Verbindungen zu beschleunigen, und verschiedene Batch-Prozesse zu steuern. Bislang wurden sie in der Automatisierung von Test- und Messinstrumenten nur selten verwendet, vermutlich wegen der Weiterentwicklung der ATE-Systeme. In den neuen SMU-Designs von Keithley wird ein Test-Script-Prozessor (TSP) mit einem schnellen Testsequenzer und einem Steuerbus (TSP-Link) kombiniert, so dass bei mehreren SMU-Systemen größere Durchsatzsteigerungen als bei einem einkanaligen Sequenzer erreicht werden können. Im System können mehrere über TSP-Link verbundene SMUs für simultane mehrkanalige Tests genutzt werden, wie wenn sie zur gleichen physikalischen Einheit gehören würden, ganz im Gegensatz zu einem sequenziellen Zugriff auf mehrere SMU-Kanäle.

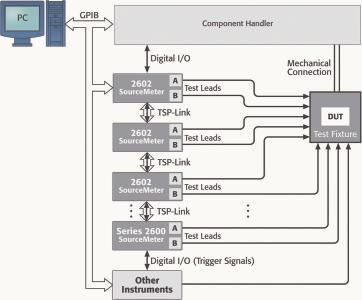

TSP-Link ist eine externe Backplane, die als Master-Slave Trigger-Synchronisations-/Kommunikationsbus zwischen den einzelnen Geräten dient, während TSP Scripte ausführt, die alle Aspekte eines Testablaufs abdecken (Bild 1). Hierfür ist kein PC-Steuerrechner erforderlich. Diese Lösung bietet alle Möglichkeiten von Befehlsaufrufen und Quellenspeicher, mit zusätzlichen Möglichkeiten zur Automatisierung von parallelen SMU-Kanälen. Ein aus einem oder mehreren Geräten bestehendes SMU-System kann mit TSP programmiert werden und eine einzelne schnelle Testsequenz oder ein beliebiges gespeichertes Testscript ausführen. Damit stellt die Koordinierung von mehreren SMUs während der Testsequenzen keine Herausforderung mehr dar. Das Ergebnis ist eine riesige Geschwindigkeitsverbesserung gegenüber einem typischen PC-gesteuerten System mit GPIB-Instrumenten auf der Basis von Microsoft Windows.. Damit ist es mit Mainframe-basierenden Systemen vergleichbar.

Reduzierter Einbauplatz: Die Geräte werden in einem 2 HE Gehäuse ausgeliefert, das nur die halbe Rack-Breite benötigt, und somit eine deutlich bessere Rack-Dichte ermöglicht. Aus praktischen Gründen haben die meisten der auf diesem Design basierenden Systeme 16 oder weniger Kanäle, lassen sich aber auf 128 Kanäle erweitern. Dies ist ein wichtiger Aspekt, da die Bauteilkomplexität und Pinzahlen weiter steigen, und damit mehr Testkanäle benötigt werden. In diesem Zusammenhang ist eine Unterbringung von mehr Geräten bei weniger Platzbedarf entscheidend, um die Produktionskosten senken zu können. Zudem ist so eine Realisierung skalierbarer und einfach zu integrierender Rack-and-Stack-Testsysteme möglich.

Kürzere Entwicklungsdauer: Die Zeit der Testingenieure ist eine wertvolle Ressource, die normalerweise mit bis zu 100.000 Dollar pro Jahr kalkuliert werden kann. In komplexen Testsystemen macht die Softwareentwicklung immer einen großen Teil der gesamten Systemkosten aus. Dies gilt besonders für proprietäre Mainframe-basierende Systeme. Die TSP-basierende Softwarestruktur bietet dagegen eine sehr viel einfachere Programmierschnittstelle für Testsequenzen in Open-API-Instrumenten. Damit ist eine einfache Erstellung von Testsequenzen über mehreren SMUs und Kanäle möglich, wie wenn diese zu einer einzigen Einheit gehören würden.

Für einige spezielle Anwendungen, wie für den Test von Halbleiter-Wafern, bieten die mit Parameter-Testern mitgelieferten vorbereiteten Testroutinen gewisse Vorteile. Andererseits ist ein TSP-basierendes SMU-System sehr flexibel und kostengünstig. Mehrere SMUs lassen sich nahtlos zu einem skalierbaren „Mainframe-losen“ System integrieren, das den hohen Durchsatz eines mehrkanaligen, Karten-basierenden Systems erreicht. Überdies kann auf steigende Testanforderungen einfach mit einem Minimum an Änderungen der SMU-Hardware reagiert werden. Es ist damit eine Standardisierung auf ein oder zwei SMU-Modelle möglich, die dann einfach durch eine Änderung der Testscripts neue Aufgaben übernehmen können.

Niedrigere Folgekosten: Ein Rack-and-Stack SMU-System benötigt keinen Mainframe-Overhead, und kommt dadurch mit geringeren Hardwarekosten aus. Da sich die SMU-Hardware bei geänderten Testanforderungen wiederverwenden lässt, reduzieren sich dadurch auch die Folgekosten. Eine Reduzierung der Entwicklungszeit für die Anwendungssoftware hat die gleichen Auswirkungen.

Auch durch den geringeren Platzbedarf in der Produktion ergibt sich im Allgemeinen eine Reduzierung der Folgekosten. Beispielsweise kalkulieren die Halbleiterhersteller normalerweise mit Kosten von 1000 bis 4000 Dollar pro Quadratmeter Produktionsfläche. Bei den rasch zunehmenden Pinzahlen der heutigen komplexen Bauteile, hat dies entscheidende Auswirkungen. Höhere Pinzahlen führen oftmals dazu, dass bei der Überarbeitung von älteren Systemen zwei oder mehr Racks zusätzlich hinzukommen. Somit kann ein Design mit höherer Dichte große Einsparungen bei der teureren Produktionsfläche ermöglichen, wenn das Testsystem dadurch auf ein Rack beschränkt bleiben kann. Dies ist mit einem Karten-basierenden System ebenfalls nicht möglich. Normalerweise sind Mainframes erst dann kostengünstig, wenn die meisten oder alle Kartensteckplätze belegt sind.

Wichtige SMU-Merkmale

Neben den typischen SMU-Merkmalen bieten die System-SourceMeter-Instrumente 2601 und 2602 Funktionen, welche die Möglichkeiten bei I-V-Tests deutlich erweitern. Beispielsweise wird der weite Dynamikbereich bei den neuen SMUs nun durch die Möglichkeit einer nahtlosen Messbereichsänderung ergänzt. Gerade die Messbereichsumschaltung kann viel Zeit in Anspruch nehmen, so dass nahtlose Messbereichsänderungen bei Testsequenzen, die mehrere Messbereiche erfordern, zu einer merklichen Beschleunigung führen können.

Die meisten SMUs verfügen über eine Stromversorgung, ein DMM und eine Vorspannungsquelle, nun kommen bei den neuen Geräten ein Impulsgenerator und Signalgenerator für niedrige Frequenzen hinzu, die auf jeden SourceMeter-Kanal geschaltet werden können. Dies vereinfacht komplexe Testanforderungen, da nun universelle analoge I/O-Pins für unterschiedlichste Anwendungen für aktive und passive Komponenten zur Verfügung stehen.

Durch die TSP-Link-Technologie in den SMUs stehen interne Triggerleitungen und ein serielles 100 MBit Bussystem, das parallele I-V-Funktionen über mehrere Geräte mit einen geringen Trigger-Jitter ermöglicht und das für Anwendungen mit hoher Bandbreite entscheidend ist, zur Verfügung.

Der TSP nutzt eine unkomplizierte Befehlssprache, die BASIC ähnlich ist. Diese dient als einfache Programmierschnittstelle für die Entwicklung leistungsfähiger, schneller, mehrkanaliger Tests, wobei die Systementwicklungsdauer merklich reduziert werden kann. Die SourceMeter-Instrumente beinhalten zudem das Softwarewerkzeug Test Script Builder, das auch Beispielprogramme in der Form von TSP-Test-Scripts umfasst. Erste Studien haben gezeigt, dass durch den Einsatz von TSP und durch diese Softwarewerkzeuge die Entwicklungszeit gegenüber den bisherigen Generationen von Instrumenten mit Testsequenzen um den Faktor zwei bis vier reduziert werden kann.

Die Modelle 2601 und 2602 wurden speziell im Hinblick auf die Anforderungen der Elektronikhersteller entwickelt, die kostengünstige automatische Systeme für den Produktionstest von Bauteilen mit hohen Pinzahlen oder den parallelen Test mehrerer Bauteile benötigen. Durch den Einsatz dieser SMUs lassen sich bestehende Testlösungen einfach mit neuen Möglichkeiten und einer höheren Kapazität ausstatten, oder durch eine minimale Investition weitere Testlösungen hinzufügen. Möglich wird dies durch die einfache Skalierbarkeit, einfachere Systemintegration und die kleinere Systemgrundfläche. Mit Testsystemen auf der Basis dieser SourceMeter-Instrumente lässt sich eine Senkung der Folgekosten, bei gleichzeitig höherer Flexibilität, Leistungsfähigkeit und Zuverlässigkeit, erreichen.

EPP 472

Vorteile der Testablaufsteuerung bei SMUs

Beim Umstieg von individuellen Quellen- und Messinstrumenten auf SMUs ergibt sich die größte Durchsatzsteigerung durch einen völlig anderen Ansatz der Systemprogrammierung. Anstelle einer PC-basierenden Steuerung erfolgt diese über die integrierte Testablaufsteuerung und den Programmspeicher des SMUs. Diese nutzt die Vorteile der SMU-Funktionen, wodurch die Testausführung vereinfacht und beschleunigt werden kann:

- Vierquadrantenbetrieb (arbeitet entweder als Quelle oder als Senke, mit positiver oder negativer Spannung oder Strom.

- Integrierte Spannungs- und Strom-Wobbelfunktion.

- Große dynamische Spannungs- und Strombereiche.

- Schnelles Einschwingverhalten.

- Empfindlichkeit im Picoampere-Bereich.

- Hohe 6½-stellige Auflösung.

- Großer Speicher (normalerweise für bis zu 100 Testfolgen).

- Eingebauter Komparator für schnelle Pass/Fail-Tests.

- Digitale I/Os und Verbindung zu Bauteilhandlern zur Bauteilklassifizierung.

Durch alle diese Funktionen in einem einzigen Gerät bleibt für Testsystementwickler weniger zu integrieren. Durch diesen Funktionsumfang ist die Testablaufsteuerung der SMUs äußerst leistungsfähig, und ein einzelnes Instrument bietet mehr Möglichkeiten. Um zu zeigen, wie sich mit dem Programmspeicher und der Testablaufsteuerung einer SMU Tests beschleunigen lassen, wurde im Zuge einer Studie ein einkanaliges SMU programmiert, um eine typische Source-Measure-Sequenz intern auszuführen. Zum Vergleich wurde die gleiche Sequenz von einem PC-Programm über den GPIB-Bus gesteuert.

Die Testfolge bestand aus drei einfachen Tests an einer Diode: Vf, Vbr und Ir. Zuerst wurde ein PC-Programm in Visual Basic erstellt, welches das SMU über den GPIB-Bus steuert, die drei Tests ausführt und die Pass/Fail-Entscheidungen mit dem VB-Programm durchführt. Alle SMU-Messwerte wurden dem PC über den GPIB-Bus zurückgegeben. Das System konnte die Diodentests und die Pass/Fail-Entscheidungen innerhalb von ungefähr 250 ms ausführen.

Anschließend wurde das System neu konfiguriert, wobei die eingebaute Testsequenzierung der SMU benutzt wurde. In diesem Fall wurde das Instrument einmal über das PC-Programm vorkonfiguriert, dann erfolgten unabhängig vom PC-Programm und dem GPIB-Bus die Source-Measure-Tests, die Pass/Fail-Entscheidungen und die Steuerung des Bauteilhandlers durch die SMU. Dieses neue System konnte die Tests in ungefähr 25 ms, d.h. gegenüber der anderen Testkonfiguration zehnmal schneller, ausführen. Der Bauteilhandler benötigte ungefähr 180 ms pro Bauteil, so dass die Testsequenzierung der SMU zu einer Durchsatzverbesserung von 52% führte. In einer Fertigungsanwendung lassen sich somit die Testkosten halbieren.

In einem einkanaligen System, wie dem eben beschriebenen, lässt sich die Testablaufsteuerung einfach nutzen und arbeitet problemlos. In Systemen, die zwei oder mehr Kanäle benötigen, kann die Konfiguration der Testablaufsteuerung, der verschiedenen Triggermodelle und der externen Triggerung äußerst komplex, wenn nicht sogar unmöglich werden. Allerdings wurde auch dieses Problem inzwischen durch eine neue Klasse von SMUs mit Test-Script-Prozessor und schnellem Steuerbus gelöst, das eine einfache Skalierbarkeit für mehrere Kanäle und eine einfache Programmierung bietet. Diese Merkmale erlauben die Ausführung selbst komplexer und schneller Testsequenzen durch die gemeinsame Nutzung der SMU-Ressourcen des Systems.

Unsere Webinar-Empfehlung

Im Webinar wird auf die individuellen Anforderungen an den Einsatz von AOI-Systemen speziell in kleinen und mittleren Elektronikfertigungen eingegangen. Durch die Beantwortung konkreter, fertigungsrelevanter Fragen bietet es einen besonders praxisnahen Inhalt.

Teilen: