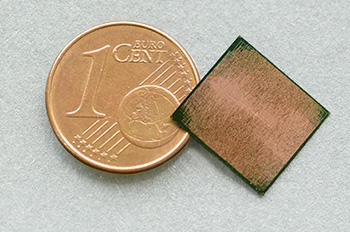

Der Institutsteil Entwurfsautomatisierung EAS des Fraunhofer IIS stellt einerseits die Software Coside vor, die Entwicklern zukunftsweisende Möglichkeiten in der Simulation und Modellierung von hochkomplexen technischen Produkten eröffnet. Andererseits steht eine neue Methode zum Entwurf von Interposern für innovative 3D-integrierte Schaltungen im Fokus. Die Forscher präsentieren unter anderem den Prototypen eines Interposers, der die kompakte Anordnung eines Prozessors und eines Wide I/O-Speichers mit hoher Bandbreite innerhalb eines ICs ermöglicht. Beides ist essentiell für das Erreichen von besonders großen Systemleistungen. Um einen solchen leistungsfähigen Interposer zu entwickeln, sind andere Entwurfsabläufe als für herkömmliche IC-Aufbauten notwendig. Das Fraunhofer IIS/EAS hat deshalb einen neuen Designflow für das Interposerdesign und die 3D-Integration erarbeitet. Außerdem bieten die Forscher Unternehmen Unterstützung bei der Wahl der für sie geeigneten Technologie zur Systemintegration an. Durch ihre semi-automatisierten Methoden lässt sich bereits in frühen Designphasen entscheiden, ob eine Applikation am besten als System-in- Package, als gehäuselose Chips auf Silizium-Interposern oder als gestapelte Chips umgesetzt werden sollten. Daneben ist es möglich, die Leistungsfähigkeit der Entwurfsumgebung Coside zu erfahren, mit der Entwicklerteams besonders hohe Anforderungen im Bereich des System Level Designs meistern können. Denn für sie wird vor allem die Komplexität heterogener Systeme, die immer öfter aus verschiedenartigen Hardware- und Softwarekomponenten bestehen, zur Herausforderung. Die Software eröffnet Unternehmen die Vorteile sowohl der freien Modellierungssprache SystemC als auch ihrer analogen Erweiterung AMS. Als wichtigste aktuelle Neuerung stellt man die Integration der UVM-Implementierung vor, wodurch diese derzeit leistungsfähigste Verifikationsmethodik auch für SystemC und SystemC AMS zur Verfügung steht. Damit ist es das erste Softwaretool weltweit, das eine solche Integration anbietet. Darüber hinaus verfügt die Entwurfsumgebung über weitere umfangreiche Funktionen, um Gesamtsysteme mit SystemC AMS extrem schnell zu simulieren und anhand von Verhaltensmodellen zu verifizieren. Der breite Funktionsumfang reicht vom nutzerfreundlichen Schaltplaneditor und leistungsfähigen Waveviewer bis zur Möglichkeit des IP-geschützten Modellaustauschs und Hardware-in-the-Loop- Simulationen. Dabei kann die Entwurfsumgebung mit zahlreichen Standard- Entwurfssoftwaretools gekoppelt und implementiert werden. Umfassender Modellierungssupport, Verifikationsservice oder kundenspezifische Schnittstellen runden das Portfolio des Fraunhofer IIS/EAS zum Entwurf heterogener Systeme ab.

Unsere Webinar-Empfehlung

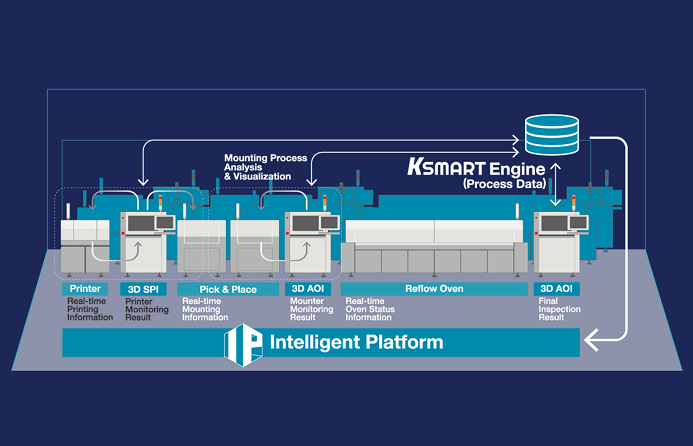

Die Nutzung der 3D-Mess- und Prozessdaten bringt die Produktionssteuerung auf die nächste Stufe. Echte 3D-Messung ermöglicht KI-basierte Prozessmodellierung zur Vorhersage von Parameteränderungen und -defekten oder zur Ursachenanalyse bis hin zu einzelnen Werkzeugen und Best…

Teilen: