BiSn-Lote, einschließlich BiSn-Eutektikum, BiSnAg-Eutektikum, BiSn-Off-Eutektikum und deren Modifikationen, wurden intensiv untersucht und gelten als führende Kandidaten für einen Niedrigtemperatur-Lötprozess. BiSn-Lot hat eine eutektische Temperatur von 138°C, was ein Reflow-Löten bei niedrigen Temperaturen ermöglicht. Allerdings schränkt die niedrige Schmelztemperatur auch den Einsatztemperaturbereich ein. Darüber hinaus birgt die inhärente Sprödigkeit von Bi das Risiko der Drop-Shock Zuverlässigkeit, insbesondere in Mobiltelefonanwendungen.

Das eutektische SnIn-Lot hat eine Schmelztemperatur von 118°C, wodurch noch niedrigere Löttemperaturen möglich sind. Folglich wäre auch die Einsatztemperatur niedriger. Das SnIn-System ist von Natur aus duktil und weich und sollte im Vergleich zum BiSn-System eine höhere mechanische Schockfestigkeit aufweisen. Um die Lotpaste bei niedrigeren Temperaturen (d. h. 190°C~210°C) reflowlöten zu können und eine Schmelztemperatur über 180°C für höhere Einsatztemperaturen beizubehalten, wurde die DFLT-Paste mit einer patentierten Technologie[2] entwickelt, die sowohl ein niedrigschmelzendes SnInAg-Lotpulver als auch ein Sn-reiches Lotpulver in der Paste enthält. Das Vorhandensein des niedrigschmelzenden SnIn-Lotes in DFLT ermöglicht das Reflowlöten bei relativ niedrigen Spitzentemperaturen bis zu 200°C oder sogar 190°C [3]. Das Sn-reiche Lotpulver löst sich während des Reflowlötens kontinuierlich in der SnIn-Lotschmelze und verschiebt die Legierungszusammensetzung in Richtung des Sn-reichen Endes. Nach der Erstarrung ist in der Verbindung keine niedrigschmelzende SnIn-Eutektikumsphase mehr vorhanden. Infolgedessen steigt die Schmelztemperatur der fertigen Verbindung auf 180°C oder sogar darüber.

Bei einem Temperaturprofil von 200°C zeigten DFLT-Pasten ein vergleichbares oder besseres Drop-Shock-Verhalten als SAC305-Pasten, die mit dem üblicherweise verwendeten 240°C-Reflowprofil gelötet wurden[3]. Zusammen mit der vergleichbaren TCT-Leistung im Vergleich zu SAC305 wurde DFLT erfolgreich für das Stapeln von zwei vorbestückten Leiterplatten durch einen Interposer in einem Stufenlötprozess mit einem Spitzentemperaturprofil von 200°C eingesetzt[2,4].

Die Automobilindustrie, aufkommende Elektrofahrzeuge und Wafer-Level-Packages mit kleineren Pitch-Größen erfordern eine höhere Zuverlässigkeit der Lötverbindungen, d. h. eine längere Lebensdauer und/oder das Überleben unter aggressiveren Betriebsbedingungen als bei den herkömmlichen SAC305-Loten. Gegenwärtig enthalten die meisten hochzuverlässigen Lote mindestens vier Elemente anstelle von nur Sn, Ag und Cu, um die Lote durch eine oder eine Kombination von Lösungsaushärtung, Ausscheidungsaushärtung und Korn-/Mikrostrukturverfeinerung weiter zu verstärken. Indium (In) ist eines der Elemente, das in der Lage ist, die Sn-Matrix durch eine feste Lösung, eine In-reiche Phase und IMC-Partikel zu verstärken, die sich mit Sn und Ag verbinden, um Ag (SnIn) IMC-Partikel zu bilden.

Frühere interne Zuverlässigkeitsuntersuchungen an WLP256 (SAC305-Kugel, 0,25mm Durchmesser) zeigten einen negativen Einfluss auf die TCT-Zuverlässigkeit bei Verwendung von starren Hochzuverlässigkeits-Loten. Die höhere Belastung durch CTE-Inkonsistenzen zwischen Si-Chips und Leiterplatten und die unzureichende Duktilität der starren Lötverbindungen wurden auf die geringere Lebensdauer im Vergleich zu SAC305 zurückgeführt. Bei der Montage von Chipwiderständen zeigte DLFT eine geringere Degradation der Scherfestigkeit der Verbindung während des TCT als SAC305, obwohl es weicher als SAC305 ist[3–4]. Dies führte zum aktuellen Versuch, DFLT – das weiche Lot anstelle des steifen Lotes – zur Untersuchung der Zuverlässigkeitsleistung an WLP256 zu verwenden. Darüber hinaus wurde DFLT als Niedertemperaturlot entwickelt, das über 200°C lötbar ist. Der Einfluss von Reflow-Profilen (Peak-Temperaturen zwischen 200°C und 240°C) auf die Zuverlässigkeit wurde ebenfalls berücksichtigt und in die aktuelle Studie integriert. Ziel des Tests ist es, zu bestätigen, dass DFLT bei einer wesentlich niedrigeren Temperatur als SAC305 gelötet werden kann, um Energie zu sparen und SAC305 hinsichtlich der Zuverlässigkeit sowohl bei Drop-Shock als auch bei TCT zu übertreffen.

Versuchsaufbau

Die Drop-Shock-Tests wurden an einem kundenspezifischen 10×10 Drop-Shock-Aufbau durchgeführt. Sowohl das BGA als auch die Leiterplatte hatten ein kreisförmiges OSP-Pad mit einem Durchmesser von 0,55 mm und einem Pitch von 2,54 mm. Die Größe des BGA betrug 50,8×50,8mm und die der Leiterplatte 101,6 mm x 101,6 mm. Die Dicke des BGA und der Leiterplatte betrug jeweils 1,54 mm.

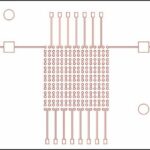

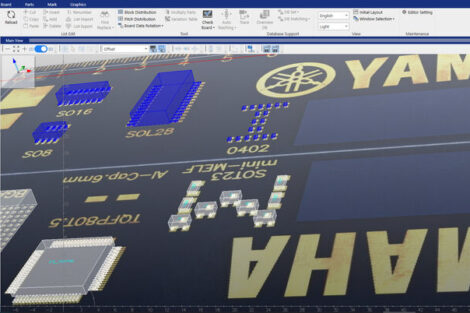

In der TCT-Studie wurde ein daisy-chained WLP256 verwendet. Die Chipgröße des WLP256 betrug 6,4 mm x 6,4 mm, der Durchmesser der SAC305-Kugel betrug 0,25 mm und der Abstand betrug 0,4 mm. Die Leiterplatte hatte ein NSMD-OSP-Pad mit einem Durchmesser von 0,3 mm. Das Leiterplattendesign ermöglichte die elektrische Dauerprüfung jeder Spalte über die rechteckigen Pads und die elektrische Dauerprüfung der gesamten Baugruppe über die beiden quadratischen Pads. Jede Baugruppe wurde an den Datenlogger für die in-situ-Durchgangsprüfung angeschlossen.

Schablonendesign

Für das Drop-Shock-Package wurde die SAC305-Paste auf der BGA-Seite mit einer Schablone von 0,102 mm Dicke und einer kreisförmigen Öffnung von 1,77 mm Durchmesser gedruckt. Auf der Leiterplattenseite wurde die Paste mit einer Schablone von 0,1016 mm Dicke und einer kreisförmigen Öffnung von 0,889 mm Durchmesser gedruckt. Mit diesem Schablonendesign wird das Lotvolumenverhältnis zwischen PCB und BGA für jede Verbindung nach dem Umschmelzen etwa 1:4 betragen,

Für WLP256 wurde DFLT-Paste auf eine Leiterplatte mit einer 0,06 mm dicken Schablone und einer kreisförmigen Öffnung mit einem Durchmesser von 0,22 mm gedruckt. Auf diese Weise wird das Volumenverhältnis von Paste zu Lotkugel konstant bei etwa 1:4 gehalten (das Verhältnis von Lotlegierung aus Paste zu Lotkugel beträgt 1:8).

Reflowlöten

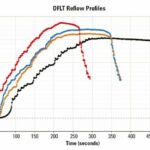

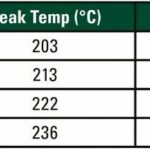

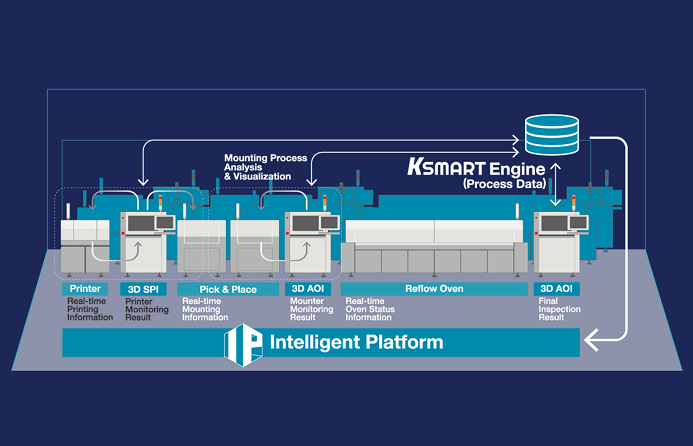

Nach dem Platzieren der Drop-Shock-BGA-Chips oder der WLP256-Chips auf den entsprechenden mit Paste bedruckten Leiterplatten wurden verschiedene Profile zum Löten der DFLT-Paste verwendet. Die Spitzentemperaturen der verwendeten Profile lagen bei ca. 200°C, 210°C, 220°C und 240°C. Als Kontrolle wurde SAC305-Paste verwendet, die unter dem Peak-Profil von 240°C gelötet wurde. Es ist zu beachten, dass das Löten bei niedrigeren Peak-Temperaturen möglicherweise nicht ausreicht, um die SAC305-Kugeln vollständig aufzuschmelzen und homogene Verbindungen mit der LTS-Paste zu bilden. Für niedrigere Peak-Temperaturen wurde ein Plateau-Profil verwendet, bei dem die DFLT-Paste ausreichend Zeit hatte, zu schmelzen und mit den SAC305-Kugeln zu verschmelzen.

Drop-Shock-Test

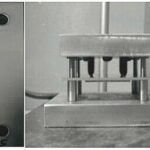

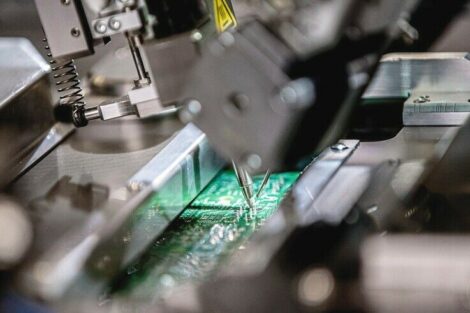

Zur Untersuchung der mechanischen Stoßfestigkeit der Lötstellen wurden Ball-Drop-Tests durchgeführt. Die Abbildung auf Seite 60 zeigt den Testaufbau und die Anordnung des Falltesters. Das gelötete Drop-Shock-Package wurde mit dem BGA-Chip nach unten auf die Probenhalter geladen. Ein Metallblock wurde dann oben auf die Leiterplatte gelegt, mit vier Stahlstiften an den vier Ecken des BGA-Bauteils (Mitte) gezeigt. Eine Stahlkugel wurde dann aus einer vorbestimmten Fallhöhe auf den oberen Teil des Metallblocks fallen gelassen, und die Stoßbelastung wurde über die vier Stahlstifte auf die Leiterplatte übertragen. Die Anzahl der Stöße wurde automatisch gezählt, bis der BGA-Chip von der Leiterplatte fiel und den Stopp auslöste. Mit dem Beschleunigungsmesser und dem Dehnungsmessstreifen in der Mitte der Leiterplattenoberfläche wurden die Beschleunigung und die mechanische Dehnung aus dem ersten Aufprall (die Kugel prallte mehrmals auf der Leiterplatte auf und ab) aufgezeichnet und in der Tabelle zusammengefasst (Fallhöhe: 500mm und Gewicht der Stahlkugel: 110 g). Jeder Datenpunkt in der Tabelle wurde aus zehn Fallversuchen gemittelt.

Thermischer Zyklustest

WLP256-Bauteile, die in Reihe geschaltet waren, wurden in eine TCT-Kammer geladen, die ein Profil von –40°C bis 125°C mit einer Verweilzeit von 20 Minuten an beiden Temperaturenden aufwies. Zur Aufzeichnung der Widerstandsänderung wurde ein Datenlogger verwendet. Ein Versagen wurde gezählt, wenn der Widerstand um 100 % anstieg. (Fortsetzung folgt…)

productronica, Stand A4.309

Verweise

[1] Hongwen Zhang, et al., “An Alternative Lead-Free Low-Temperature Solder with Excellent Drop Shock Resistance,” Proceedings of SMTA International, 2020, pp.280–290.

[2] Hongwen Zhang, et al., “Low-Temperature Melting and Mid-Temperature Melting Lead-Free Solder Paste with Mixed Solder Alloy Powders,” Patent application, US 2020/0353572 A1.

[3] Baker, H., et al. (1990). ASM Handbook, Volume 3: Alloy Phase Diagram, 2.260, ASM InternationalG.

[4] Haley Fu, et al. “iNEMI BiSn-based Low-Temperature Soldering Process and Reliability Project Report,” (iNEMI Low-Temperature Soldering Workshop, April 24, 2019).