Die Realisierung und Optimierung des künftig in der mobilen Kommunikation wichtigen Bluethooth-Standards basiert auf profunden, aufeinander abgestimmten Lösungen in der Entwicklung von Produkt, IC und Substrat, wobei natürlich auch die kritischen „Blauzahn“-Spezifikationen eingehalten werden müssen. Wie bei der Implementierung solch unterschiedlicher SiP-Bausteine (System-in-a-Package) die Faktoren für Kosten und Größe zu berücksichtigen sind – wobei als Substrat LTCC (Low Temperature Co-fired Ceramic, grüne Keramik), Glas sowie Silizium auf Silizium mögliche Alternativen sind – beschreibt diese zweiteilige Serie. Im in der EPP 3/2001 erschienen ersten Teil wurden bisher Schaltungsaufteilung, Montagemethoden und Gehäuseformen behandelt.

Douglas J. Mathews, Amkor Technology, Chandler, USA

Überlegungen zu Tests

In der vollständigen Implementierung des Bluetooth-Standards gibt es gut definierte elektrische Tests. Spezielle Prüfungen sind über das Link-Management-Protocol möglich, es erlaubt, das Modul im Loopback-Betrieb in seinen HF- und Basisbandfunktionen ausführlich zu testen. Diese Betriebsart ermöglicht, Burst-Timing und Drift, Bitfehlerrate, Dynamikbereich des Empfängers und die Leistungsteuerung des Senders zu prüfen. Enthält ein SiP nur die Basisband- und HF-Stufe, werden Tests schwieriger, weil das Equipment dann sämtliche Steuersignale und Protokolle bereitstellen muss.

Für Fertigungsprüfungen kann das Interface zwischen Schaltung und Tester problematisch sein. Für die hochvolumige Fertigung und Prüfung sind automatische Handling-Systeme wesentliche Voraussetzung. In unmittelbarer Nähe des Moduls darf sich wegen der Auswirkungen auf die Ausbreitung der Funkwellen möglichst wenig Metall befinden. Die Kontakte zwischen Modul und Adapter müssen HF-geeignet sein und sehr gerin-ge Induktivitäten aufweisen, also möglichst kurz sein. Es gilt die Impedanz der HF-Leitungen sorgfältig zu kontrollieren, um Signalreflektionen zu vermeiden. Um Rauschabstände nicht zu minimieren, ist große Sorgfalt bei der Führung der analogen und digitalen Signale geboten.

Bluetooth-Module werden sowohl mit nackten als auch gehäusten Chips konfiguriert. Gehäuste Chips offerieren Vorteile bei der Prüfbarkeit, nachteilig sind Größe und Kosten. Der Test nackter Chips aber ist wegen des hier nötigen Waferprobings problematisch, zudem stellt sich die Know-Good-Die Frage (KGD).

Single-Chip- und Multi-Chip-Lösungen

Die hohe Variabilität der Implementierungen rührt nicht nur vom IC her, sondern auch von den Substraten. Bluetooth-Schaltungen werden als HF-IC-Module, Link-Controller und HF-ICs, Single-Chip und mit Flash-Speicher realisiert. Zu den IC-Varianten kommen noch unterschiedliche Substrat-Implementierungen wie Laminate, LTCC und Glas. Es ist absehbar, dass kostengünstigere Laminate mit integrierten passiven Netzwerken (IPN) auf Glas und Silizium für die wichtigsten Implementierungen zur Verfügung stehen. Verschiedene SiP-Versionen sind in Bild 9 dargestellt.

Zweischicht-Laminate sind die kostengünstigste Lösung für ein Modul gegebener Größe, aber sie fallen größer und mit höheren Streuungen aus. Die Bluetooth-Spezifikation ist sehr großzügig, sie kann erhebliche Varianzen aufnehmen, die der OTD-Schaltungsanteil einbringt. Je höher der Integrationsgrad im HF-Teil, desto besser eignen sich Laminate. Selbst dann, wenn eine OTD-Schaltung nötig ist, können Mehrlagen-Laminate trotz zusätzlicher Kosten eine gute Alternative sein.

Die Kosteneinsparung bei LTCC beruht auf den eingebetteten passiven Bauelementen in der mehrlagigen Keramik. Glas gewinnt an Popularität, obwohl die Großserienfertigung (ca. 250.000 Einheiten/ Woche) noch aussteht. Glas und Silizium lassen sich als IPN-Substrat verwenden, wobei eine Vielzahl von Kondensatoren, Widerständen und planaren Induktivitäten auf kleinerem Raum und mit geringer Streuung realisierbar sind. Beide erfordern entweder Drahtbonden des Substrats zum anderen Substrat oder die invertierte BGA-Implementierung. Bei einem umgedrehten BGA werden die Lotkugeln an die Außenkante des Substrats verlegt, das damit größer wird.

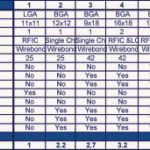

Physikalisches Modell

Zur Veranschaulichung der unterschiedlichen Implementierungen eignet sich das physikalische Modell eines auf Laminat basierenden Bluetooth-Systems. Für die Kostenanalyse werden verschiedene Parameter variiert und der Gesamtpreis eines SiPs wurde in Relation zu einem einfachen Single-Chip-Modul untersucht. Eine Variante des Modells (Nr. 5) ist in Bild 10 dargestellt. Hier wurden Basisband-Prozessor und HF-IC in einem BGA auf BT-Laminat realisiert (zwei Metalllagen getrennt durch Dielektrika). Die größere rechteckige Fläche ist eine SMD-Antenne. Der SiP enthält auch diskrete Passive für Filter und Balun-Trafos sowie drahtgebondete PIN-Schaltdioden. Diese Implementation ist ein 18 x 20 mm² großes Modul, das nicht größenoptimiert ist. Die Kosten wurden in Bezug gesetzt zur kostengünstigsten Implementierung dieses Substrats. In der Tabelle sind mehrere Lösungen und ihre relativen Kosten für einige Konstanten dargestellt: Großserienfertigung von 250.000 Einheiten/Woche; Substrat aus BT-Harz; zwei Lagen und diskretes Filter. Diese Kosten umfassen nicht den Chip und die Testausbeute.

System 1 besteht aus dem HF-IC mit externer Beschaltung (diskreter Filter, Loop-Filter, Entkopplungs- und Bypass-Kondensatoren). Es wurde als LGA mit Drahtbonding ausgeführt. System 2 ist eine Single-Chip-Lösung mit HF-IC und DSP, mit derselben OTD-Beschaltung wie System 1, aber als BGA realisiert. Die wichtigsten Unterschiede in den Kosten (abgesehen vom Chip) bestehen in Encapsulation, Lotkugeln und dem für die Abschirmung erforderlichen Platz. Die relativen Kosten liegen um den Faktor 2,2 höher als für System 1, bei ungefähr gleicher Größe und Chipzahl.

System 3 ist ebenfalls ein Single-Chip (wie Konfiguration 2), umfasst jedoch Balun-Trafos und Schalter. Das Modul ist durch OTD-Schaltung größer geworden. Die Kosten sind etwas höher als beim System 2, hauptsächlich wegen dem größeren Substrat und den passiven Bauelementen. System 4 ist identisch mit System 3, mit der Ausnahme, dass es sich um eine Zwei-Chip-Lösung handelt. Zusätzlicher Platz wird für den zweiten Chip, für Anschlüsse zum HF-IC sowie für Entkopplungs- und Bypasskondensatoren benötigt. Auch hier sind sowohl Größe und Kosten gestiegen. System 5 ist identisch mit 4, einzige Ausnahme ist die SMD-Antenne. Die Kosten sind auf das 3,8fache gegenüber System 1 gestiegen.

Als Single-Flip-Chip mit gehäusten Schaltdioden unterscheidet sich System 6 erheblich. Das Gehäuse ist erheblich kleiner, aber nicht proportional geschrumpft. Die Kosten entsprechen etwa denen des größeren Systems 5. Die Kosten sind von Prozess und Größe bestimmt. Flip-Chip-Technik ist teurer und erfordert Underfilling für den Ausgleich der unterschiedlichen Temperaturkoeffizienten. Das Substrat könnte kleiner sein, aber für die Unterfüllung wird etwas Platz um den Chip herum benötigt, um das Material zu dispensen. Die Größe des Substrats könnte mit gebondeten Dioden reduziert werden. Obwohl Flip-Chip und Drahtbonding in einem Prozess kombinierbar sind, ist das Ergebnis kostenintensiv. Ein Kompromiss in den Prozessen, Bauelementauswahl und Modulgröße könnte die Kosten minimieren. Im Vergleich zu diesem für BT-Harz geltendem Beispiel steigt die Komplexität für jedes andere Substrat immer weiter an.

Um die anvisierten Kosten einer Applikation zu erreichen, muss man nicht nur die Implementierung des ICs, sondern auch das Substrat, die OTD-Schaltung sowie die Montage- und Testmethode untersuchen. In Bild 11 sind wichtige Kostenfaktoren zusammengefasst. Sämtliche Elemente im Flussdiagramm können auch die Performance beeinträchtigen, so dass ein gutes Verständnis für die Kostenvariablen und ihre Auswirkungen auf Performance und Größe gefragt ist.

IC-Implementation und SiP-Integrationsgrad gehen auf die Gesamtkosten eines Systems ein. Unbedingt erforderlich ist, dass zuerst die Packaging-Frage beantwortet wird, vorzugsweise während des Chip-Entwurfs. Andernfalls werden wahrscheinlich höhere Kosten entstehen. Aufteilung von System und IC, Substratwahl, Implementierung der passiven Bauelemente, Montage- und Testmethoden sind die Hauptfaktoren für die Systemkosten.

Co-Design eines Systems

Der effektivste Weg für die Optimierung liegt im Concurrent Engineering (verzahnte Entwicklung) bzw. dem sogenannten Co-Design. Dem Co-Design liegt die Systementwicklung auf sämtlichen relevanten Ebenen zu Grunde: also Produkt, IC und Substrat. Dabei ist das Package ein funktioneller Bestandteil des Bluetooth-Systems. Für optimale Kosten und Modulgröße muss das Package parallel und interaktiv mit IC und Produkt entwickelt werden. Simulationen werden gemeinsam genutzt, um die erforderliche Funktionalität sicherzustellen. Verständnis der Herstellungsprozesse, Produktionstests und Design-Entscheidungen sind der Schlüssel für die Optimierung. Auch das Supply-Chain-Management in der Bauteilbeschaffung ist wichtig, denn Bezugsquelle und Zweitlieferant für sämtliche Bauelemente sind nötig. Damit mehrere Unternehmen in einer gemeinsamen Entwicklung zusammenarbeiten können, ist Programm-Management erforderlich.

Amkor Technology hat ein Programm implementiert, mit dessen Hilfe Bluetooth und andere drahtlos arbeitende Systeme per Co-Design realisiert werden können. Mit einem Komplettangebot, das von der Projektplanung bis zur Bauelemente-Entwicklung reicht, können wir Package- und Substratentwicklung in kürzerer Zeit zur Verfügung stellen. Mit profunder Kenntnis der Fertigungsprozesse und deren Auswirkungen sowie den installierten Produktionskapazitäten lassen sichen anvisierte Kostenrahmen einhalten. Zudem hat Amkor mit der Implementierung von HF-Tests sowohl auf Chip- als auch auf Modulebene begonnen. Mit unserem Equipment für digitale und Mixed-Signal-Umgebungen offerieren wir komplette Lösungen.

Das dominierende Kostenelement ist der Chip selbst. Eine Evolution der vielen Implementierungen wird notwendig sein, damit die niedrigst möglichen Chipkosten erreicht werden. Host- und Stand-Alone-Applikationen treiben die Entwicklung der Bluetooth-HF-ICs und DSP/HF-Module voran. Diese funktionelle Aufteilung wird wahrscheinlich noch weiter gehen. Auch alternative Substrate dürften ins Interesse rücken. Flexible Folien, Silizium und Glas sind wahrscheinliche Kandidaten dafür. Doch über allem steht der Ruf nach Kostensenkung, optimierten Montagemethoden und hochvolumiger Fertigung.

EPP 193

Unsere Webinar-Empfehlung

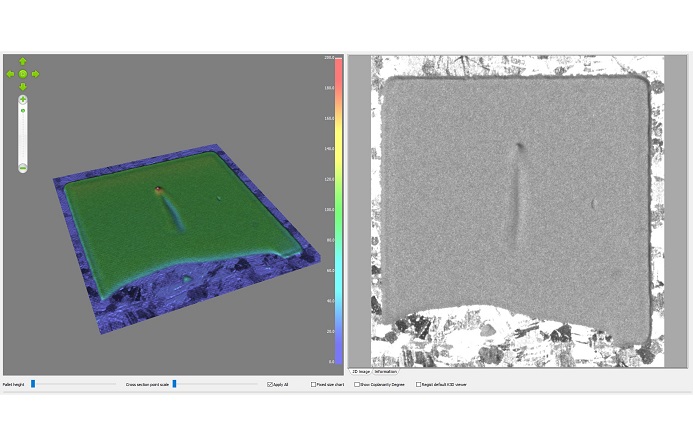

Applikationen aus dem Bereich der Leistungselektronik gewinnen immer mehr an Bedeutung. Die Inspektion dieser Applikation lässt sich mit der bewährten Standardtechnologie der 3D-Messtechnik bewerkstelligen.

Teilen: